- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

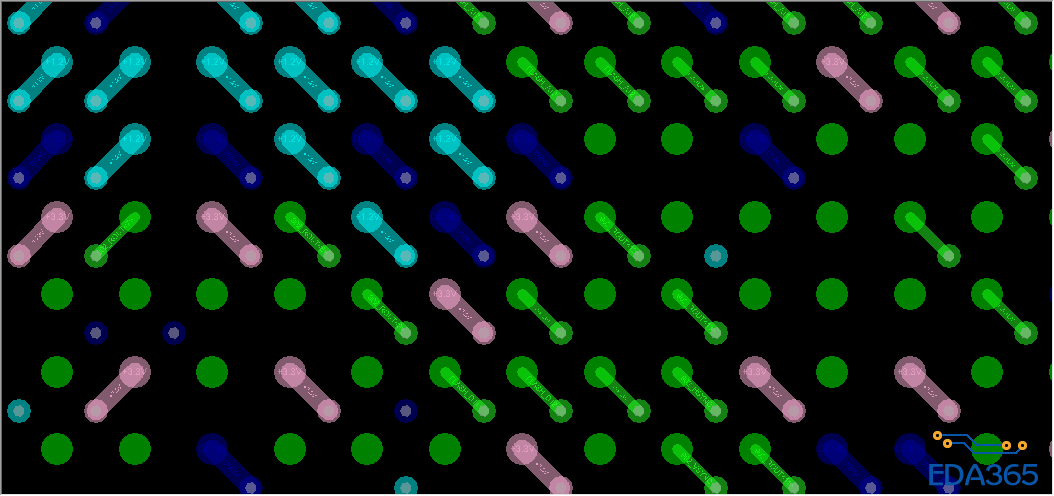

FPGA扇出问题,详细请进。

录入:edatop.com 点击:

如图,怎么才能让FPGA一次性扇出时,信号线宽和电源、地的线宽不一样啊?我现在都是先一起扇出了,然后将电源、地网络锁住,删掉信号线的扇出,然后再将信号线以不同的线宽扇出,感觉这样既笨又没有效率,请教各位大神有没有更好的方法。

我觉得应该定义电源和信号线的线宽约束,然后在Fanout的时候,选择默认网络线宽,这样就可以了

设置一个要加粗的CLASS组,然后把这个组的线宽最小设置为15MIL,你再FANOUT的时候就会为15MIL(你想要加粗的电源地网络)

设置一个要加粗的CLASS组,然后把这个组的线宽最小设置为15MIL,你再FANOUT的时候就会为15MIL(你想要加粗的电源地网络)

设置一个要加粗的CLASS组,然后把这个组的线宽最小设置为15MIL,你再FANOUT的时候就会为15MIL(你想要加粗的电源地网络)

扇出的时候没有选择默认线宽的选项,都是一样的线宽。

试了一下,可以了,但是我在连接其他的电源和地的时候线宽就被约束成和扇出的线宽一样了,可以不可以只在扇出的时候用一种线宽,一般连线的时候是默认线宽呢?

现在可以了,我软件操作还不熟。

扇出时选择create fanout,然后选择需要扇出的net就可以啦。信号线采用同样的方法。这样约束就不会冲突。

可以,你在电源地的CLASS用默认规则,设置一个区域规则,在物理规则里面有个Rigion,在这里面你能看到你所画的区域名称,在区域名称上右击,有一个Rigion_Class,然后选择电源地的Class,在这里面电源地的Class一排对应的线宽位置输入你想要的线宽,就可以了

好的,学习了,谢谢!

这么小的孔?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:有人在用16.6吗?

下一篇:铺铜遇到下面两个问题,请帮忙看看咋解决