- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

敢问哪位大侠有把PIN delay导入到BRD里面的操作文档吗?

录入:edatop.com 点击:

如题,感谢!

首先PIN delay数据文件扩展名为csv,可以用Excel编辑后另存为csv文件,格式为一列管脚编号,一列长度;

在Allegro中File->Import->Pin Delay,选择文件,点击对应器件,单击Import按钮。

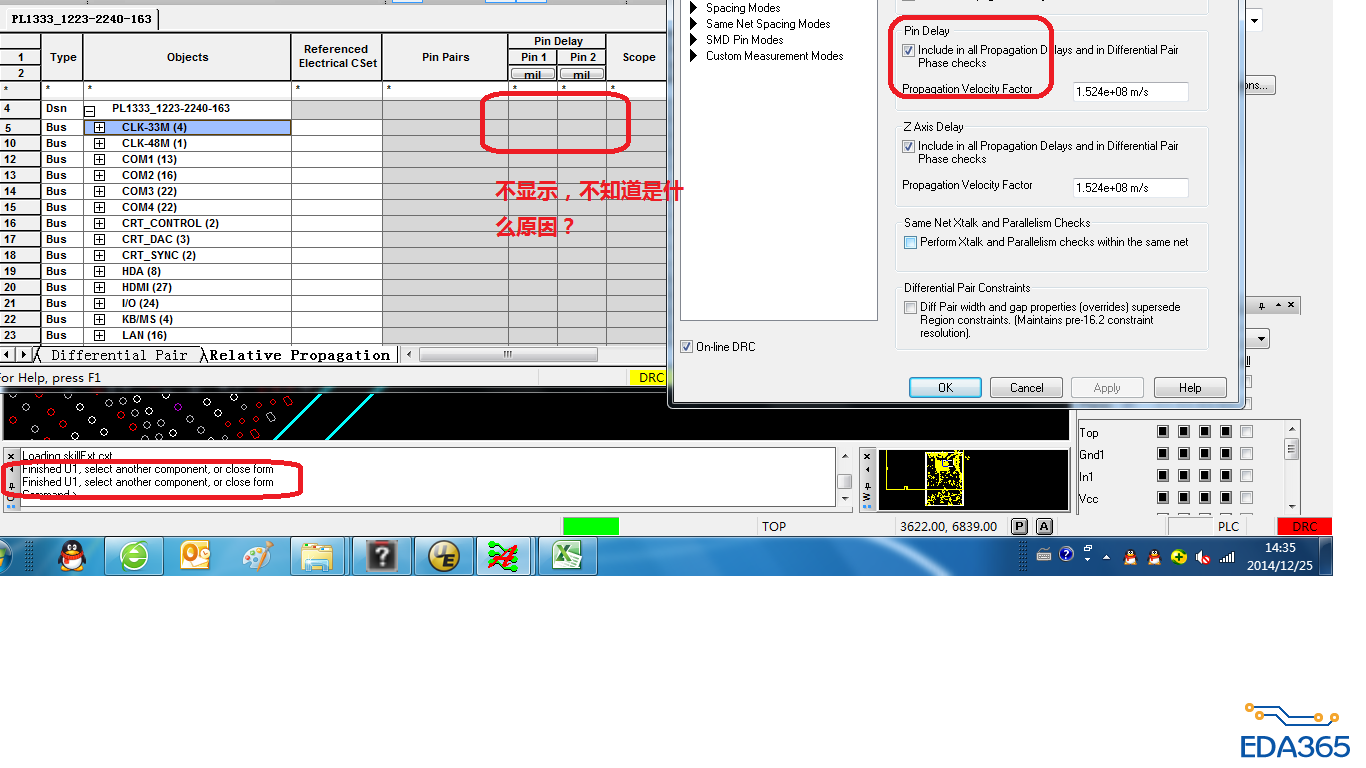

在Constraint Manager中,Analyze->Analysis Modes,打开Electrical Optoins,勾选Pin Delay下的选项,单击ok使规则生效。

好的。谢谢小编。我试试。

导入进去了不显示。不知道是不是还有其它的设置呢?

如下图

BUS上是不会显示的,要设置等长规则后才会出现。

啊。那有办法在设置match group之前显示出来吗?

先说一下你的目的。

没有什么目的,就是想知道可不可以?小编。

在Excel里面看也可以,Allegro里面可以用查询Pin的功能看报表。

导入Pin Delay无非就是为了等长,既然要做等长,那就把等长规则设上就好了,设上以后就可以直观的看到了。

哦。谢谢小编,另外想请问一下,档案降了版本后会影响吗?比如说我从16.6降到16.3以后再操作会有异常吗?感谢!

对Pin Delay无影响,具体影响看Downrev.log

恩,好的。谢谢。