- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Allegro约束在重新导入logic后会部分消失

录入:edatop.com 点击:

我在使用的Allegro16.3会出现这样一个问题,在修改原理图设计后(小改动),重新生成网表,导出netlist。Allegro导入logic,原来本来设好的约束会部分丢失,比如有些设置的差分线,有些设置在POWER的约束组里的,每次都这样,害得我每次都提前先把约束文件导出一份,导入logic后再把约束倒进来。请问大家这是怎么回事,怎么处理啊?谢谢!

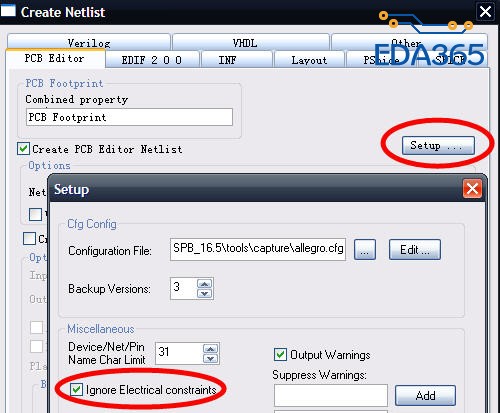

出网表的时候勾选这个选项呢。

顶起,大家遇到过这种情况么

习惯问题,因为CAPTURE和allegro是靠这些属性来传递的,然后由于早先设置,或者回注,PCB里面的约束会传递到原理图里面,然后你后面在导入网标后,修改约束,然后再修改原理图的话,重新导入后原理图里面原来的约束会覆盖掉PCB里面的,常用方法有两种:

1,新绘制原理图的时候,不要从已有的复制尽量,这样就不会有这些东西

2,如果要复制,可以删除掉原来原理图里面的没用的属性,方法是在dsn或者sch上点右键-edit obj pro ,然后就可以在flast nets和Globals里面删除没用的属性了,删除后就不会有事了

我也是遇到同样的情况,一直没找到解决方法

那现在这种情况下,要怎么处理才能解决这个问题呀,谢谢

要怎么处理才能解决这个问题?

小编正中!亲测有效