- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

0.5球间距BGA出线方式求教

录入:edatop.com 点击:

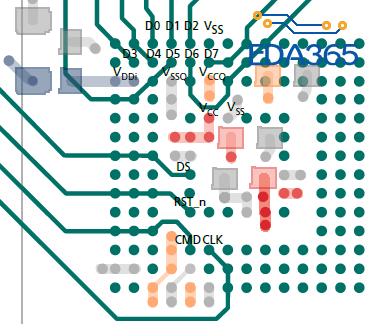

如图所示,是一颗美光的EMMC颗粒

0.5的球间距出线,应该是有点困难吧。所以官方推荐利用那一堆没用NC脚把线拉出来(这EMMC搞那么多NC脚也是醉了)

那么问题来了,这样搞的话,一定要在原理图里把需要用到的NC脚和CLK,DS,CMD的网络连起来?

0.5的球间距出线,应该是有点困难吧。所以官方推荐利用那一堆没用NC脚把线拉出来(这EMMC搞那么多NC脚也是醉了)

那么问题来了,这样搞的话,一定要在原理图里把需要用到的NC脚和CLK,DS,CMD的网络连起来?

用3mil的线从空隙走出来就行。

找个好点的板厂做。

非要从那个nc脚走也不用改原理图了,太麻烦,就直接带着drc走过去就完了

或者 在allegro里net logic?

擦,想法太多。

对对对!就是这种感觉,想法太多,举棋不定!

带着DRC应该是不行的,后面要做等长,调阻抗啥的

你自己选吧,都是解决办法。

NET LOGIC是啥?求详解

就是在allegro里直接改net的一个功能,论坛里有相关帖子的,你找下~

埋盲孔。通孔偶尔也可以打在焊盘上从内层走好啦。手机芯片都这么做的

他说那个是让你SWAP PIN

这玩意要是可编程的你直接跟硬件商量着换PIN角就好了

我就是硬件

盲埋孔就算了,四层板解决战斗

恩!好极了!这个貌似就是想要的功能实现!

在allegr里改,还不如orcad里面快呢,不知道咋想的。

直接 HDI了。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:关于约束管理器中via的问题

下一篇:Allegro16.6重启电脑后要运行License Manager->LmTools下Start/Stop/Reread