- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

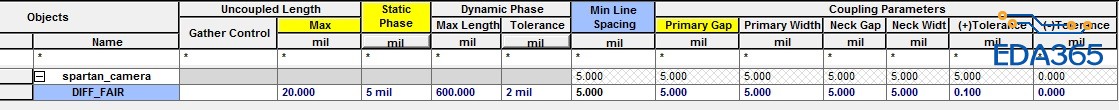

FPGA 差分线规则的设置

其中LPDDR SDRAM的时钟和HDMI都是差分设置,我做以下规则设置,不知是否可行?LPDDR SDRAM 的时钟只有200MHz。

刚知道hdmi要阻抗匹配100Ω±15%

Uncoupled length如果设置参数的话,20mil是不够的;

Dynamic Phase参数不用设;

线距/线宽(Primary Gap Primary Width)参数太小,做不到100欧阻抗,建议线距/线宽设为:7/6,后面让板厂根据阻抗要求去调整。

非常感谢小编,请问Uncoupled length设置多少为好?

另外我查了一下板厂的板材结构:

4 Layer Board Stackup and Specifications :

1 oz copper (1.4 mil)

6.7 mil prepreg

0.5 oz copper (0.7 mil)

47 mil core

0.5 oz copper (0.7 mil)

6.7 mil prepreg

1 oz copper (1.4 mil)

The substrate for both the core and prepreg is FR408, with a dielectric constant of 3.66 at 1GHz。

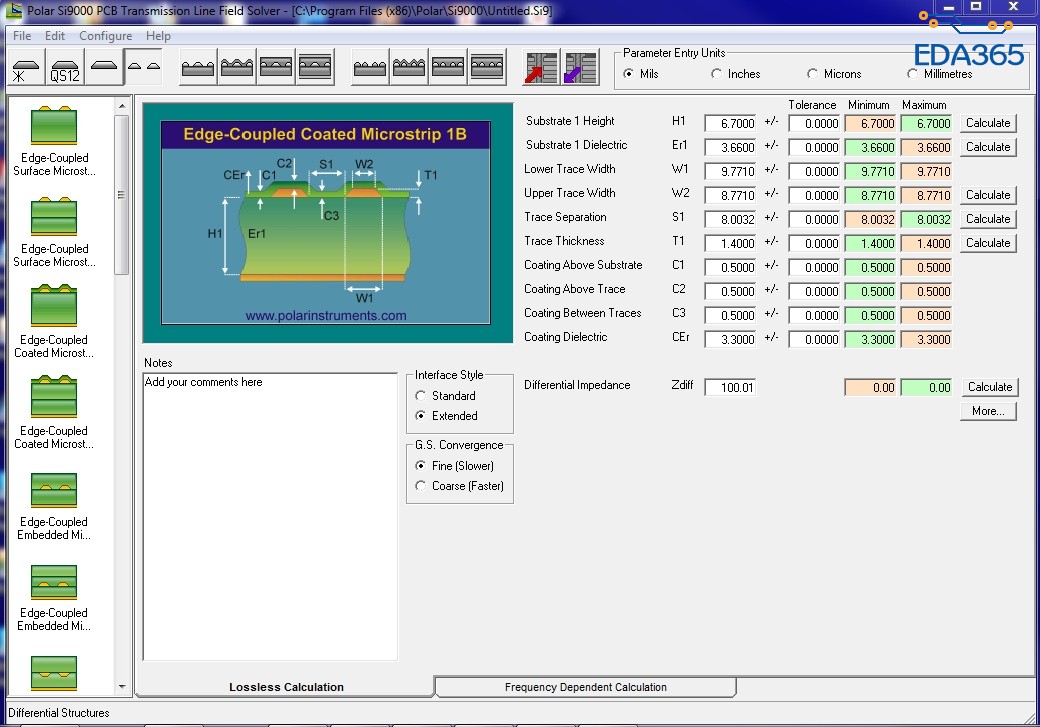

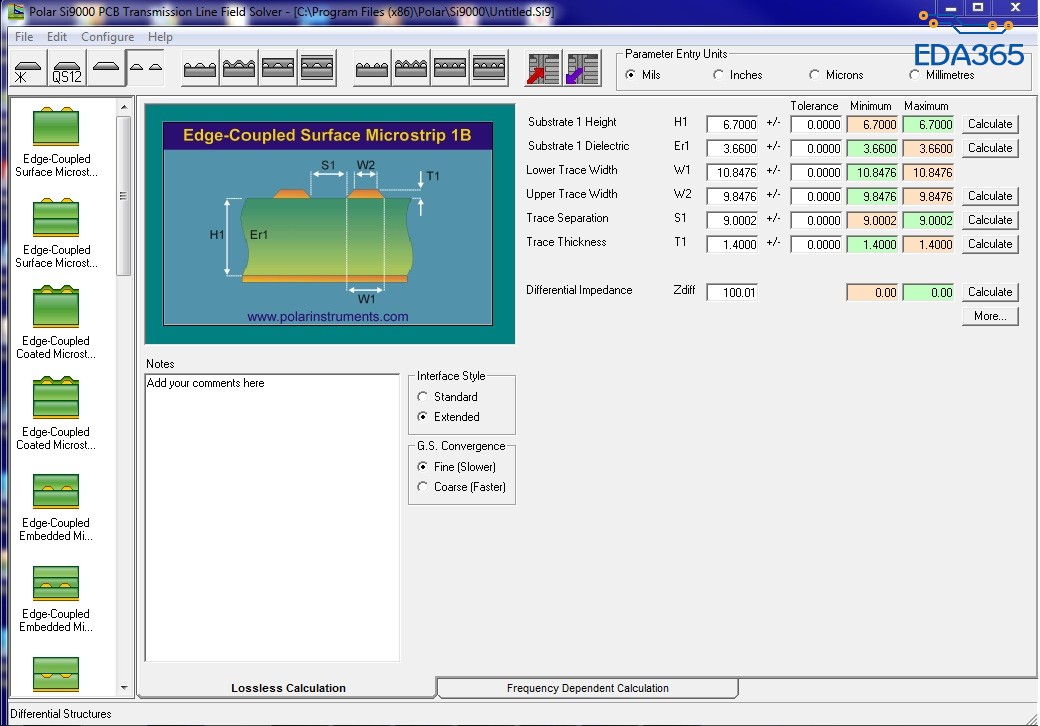

这个没提到阻焊层的信息,我用si9000计算的差分100欧阻抗匹配的时候,是要(1)Edge-Counpled Surface Microstrip 1B ---不带阻焊层;还是(2)Edge-Coupled Coated Microstrip 1B --- 带阻焊层?

(1)我分别用不带Solder mask和带Solder mask的参数算了一个, 如下图,请问我该选哪个合适?

(2)Solder mask的参数我都取了0.5. 另外,关于走线宽度我是直接取W1, 还是要W1+Etch loss?

(3)关于板材的介电常数,这个厂用的FR408, with a dielectric constant of 3.66 at 1GHz, 我查了一下

FR408的datasheet: http://www.isola-group.com/wp-co ... preg-Data-Sheet.pdf

是说3.65到3.69, 我是否直接取3.66就可以了?还是要取通用的4.2?非常感谢!

不错

理论上应该为0,实际上要看布线情况,尽量减少两根线分开的长度,使这个数值尽量小。

hdmi要阻抗匹配100Ω..

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:阿里狗17.0焊盘制作软件界面

下一篇:orcad16.6导出网表出错