- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Allegro 16.6 差分 约束 问题请教

我的板子是8层,差分线在4个信号层里走的线宽和线距是不一样的,两种不同的差分线,一个是100欧,一个是90欧

因此我想设定两个不同的差分规则,

第一个问题,约束管理器里头新建一个差分的Electrical CSet的时候,发现PrimaryWidth他只能设定一个参数,而不能设定每个层的参数如图:

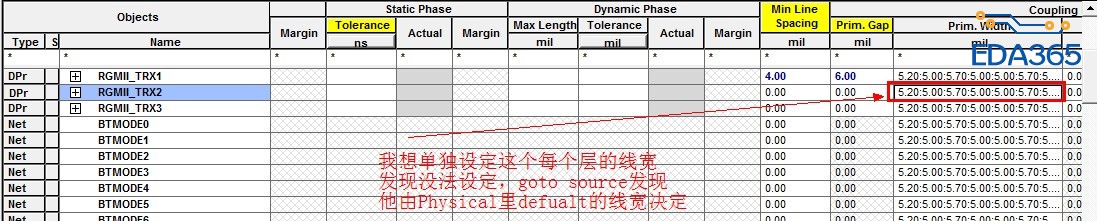

第二个问题,直接在Electrical ->Net ->Routing ->Differential Pair里编辑某个差分的Prim Width,发现这个参数由Physcial里的Default的

Physcial->Physical Cosriant Set->Defalut->Line Width ->Min决定,不知道可不可以单独编辑Electrical ->Net ->Routing ->Differential Pair里编辑某个差分的Prim Width?

不知道我描述清楚没有,不清楚我再来

没完全搞懂你遇到什么情况了,我觉得只需要弄清楚一点ELE,PHY两个里面都可以建立DP约束,但是不太一样,电气约束是电气化的,和层叠板厚没关系,物理层的约束是和层叠设置一些相关的。

所以:1,ELE CS里面是不能根据层叠来设置不同线宽的约束的;

2,不要把两个混起来用,从你goto source的结果来看,貌似哪里没对,我也不太清楚,看不到板子。

3,但是建议最简单的操作方法,比如N层板子有90,100的差分约束,如果4层板或者其他所有层线宽间距一样,不用根据板层调整,就设置ELE CS然后赋予对象,如果是当前阻抗由多种不同线宽-间距组成,就在PHY里面建立对应的约束,然后赋予对象,很简洁,当然你可以都用PHY。

建议你删除ELE里面的,然后从PHY里面设置好再试试, 应该不会有问题的

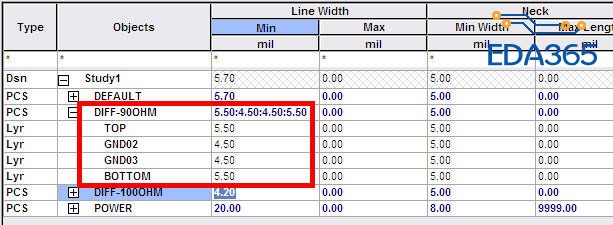

如果要分层设定差分线线宽,需要到Physcial->Physical Cosriant Set中设置,可以设置多种约束,不一定要用Default,如下图:

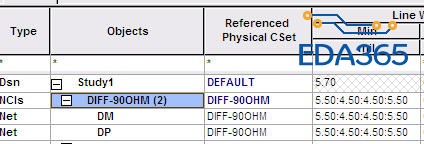

再把约束规则指定给差分线,如下图:

非常感谢各位,大致有答案了,

第一个问题 electrical 的diff cset不让单独设置每个层的线宽线距

强制设置之后出现提示:

Invaild Value ,too many fields, Selected object does not support layer specific values.

第二个问题实际给出了解决办法,就是如果想设置多层线宽线距,就只能到physcial 里头来设置

差分规则。

不清楚cadence对第一个问题是怎么想的,限制的目的和思路是什么,

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:出IPC报错,怎么弄

下一篇:如何能最近的显示飞线