- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请教:Allegro约束管理器中BUS添加NET失败。

录入:edatop.com 点击:

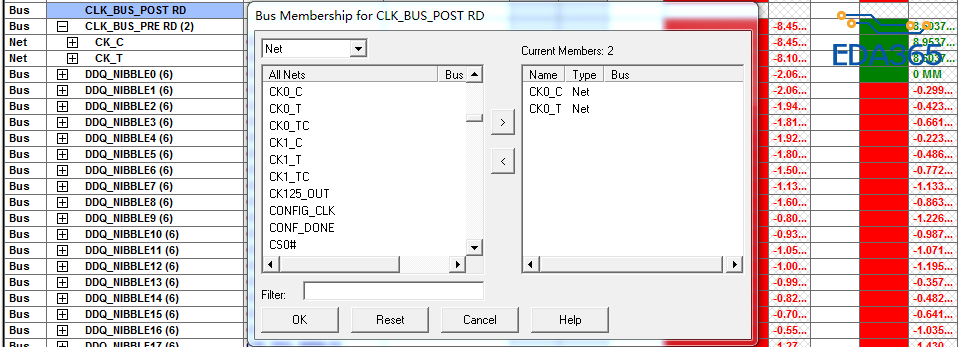

请教一个问题,烦请帮忙:1. 我在Allegro约束管理器(Constrain Manager)中添加一个BUS,如下图所示: 首先创建BUS:CLK_BUS_POST RD, 然后再把NET:CK0_C,CK0_T加入BUS中。

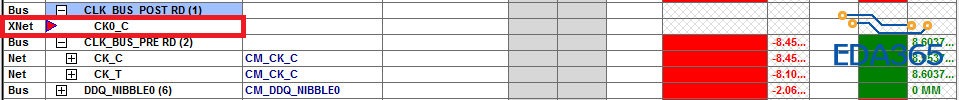

2. 确认OK后,在此CLK_BUS_POST RD下显示的只是XNet: CK0_C,而没有成功添加NET:CK0_C,CK0_T?如下图所示。请问是什么原因导致的?谢谢!

2. 确认OK后,在此CLK_BUS_POST RD下显示的只是XNet: CK0_C,而没有成功添加NET:CK0_C,CK0_T?如下图所示。请问是什么原因导致的?谢谢!

BUS不是随便创建的,BUS顾名思义总线,你在命名上必须符合总线规范。你可以建立一个class,这个是根据你需要的牟总分类依据来建立的,比如这一组都是时钟,都是复位,都是电源,都是需要走20mil宽度的,都是阻抗有50ohm需求的等等,自己想怎么分就怎么分

谢谢回复。您请看第二张图我也创建另一个BUS:CLK_BUS_PRE RD, 它就可以添加NET:CK_C,CK_T。

是不是XNet:CK0_C已经包含了这两个net?

看起来是的,但是我不知道如何来改,我试过选中CK0_C 信号,然后Edit-->Properties,选择Delete Signal_Model,现象依旧。

那我理解错了可能,不过严格意义上来说,这种划分成class是比较科学的 ,当然,只是个人习惯。

你要把XNet:CK0_C所接的分立器件模型去掉,而不是把这根信号的模型去掉。去掉分立器件模型后,这根Xnet也不存在了。

我把CK0_C接的器件模型更新就可以解决问题了。非常感谢!