- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于 signoise errors 的问题

set ads_boardrevs = 1

set ads_dbext = brd

set ads_logrevs = 4

set ads_materialname = materials

set ads_msgname = allegro

set ads_norevs = 1

set ads_textrevs = 2

set adsboardpath = E:/working/tr5 .

set adspath = . C:/Cadence/SPB_16.6/share/pcb/text

set alibpath = C:/Cadence/SPB_16.6/share/pcb/pcb_lib

set allegro_brd2odb = C:\MentorGraphics\Allegro Export ODB++

set allegro_dynam_timing_fixedpos =

set allegro_install_dir = C:/Cadence/SPB_16.6/share/pcb

set allegro_install_dll = C:/Cadence/SPB_16.6/tools/pcb/bin

set allegro_install_root = C:/Cadence/SPB_16.6

set allegro_install_tools = C:/Cadence/SPB_16.6/tools/pcb

set allegro_site = C:/Cadence/SPB_16.6/share/local/pcb

set allegro_type = pcb

set allusersprofile = C:\ProgramData

set ansifont = ansifont

set appdata = C:\Users\chenmaojie\AppData\Roaming

set aptpath = . ..

set artpath = . ..

set artwork_no_unit_warn =

set autosave =

set autosave_time = 10

set base = E:/working/tr5

set batchhelppath = . C:/Cadence/SPB_16.6/share/pcb/batchhelp

set bmppath = . C:/Cadence/SPB_16.6/share/local/pcb/icons C:/Cadence/SPB_16.6/share/pcb/text/icons

set brd_dbext = brd

set brd_mcm_tech = EXT=brd:EXTALT=mcm;tech:MSG=BRD/MCM/TECH:TITLE=Select a BRD/MCM/TECH file:

set caetbin = C:\adiva\bin

set caetdata = C:\adiva\data

set caethelp = C:\adiva\manual

set cds_lic_file = 5280@chmj

set cds_lic_only = 1

set cds_sis_msglog_key = SISMsgLog

set cds_site = C:/Cadence/SPB_16.6/share/local

set cdsdoc = algcmdref

set cdsplat = wint

set cdsroot = C:\Cadence\SPB_16.6

set cdsversion = 16.6

set chdl_lib_inst_dir = C:\Cadence\SPB_16.6

set cio_dbext = cio

set class = BOARD GEOMETRY

set clippath = .

set commonprogramfiles = C:\Program Files (x86)\Common Files

set commonprogramfiles(x86) = C:\Program Files (x86)\Common Files

set commonprogramw6432 = C:\Program Files\Common Files

set compalib = C:/Cadence/SPB_16.6/share/pcb/pcb_lib/symbols C:/Cadence/SPB_16.6/share/pcb/allegrolib/symbols

set complibpath = C:/Cadence/SPB_16.6/share/pcb/allegrolib

set computername = CHMJ

set comspec = C:\Windows\system32\cmd.exe

set concept_inst_dir = C:\Cadence\SPB_16.6

set cwd = E:/working/tr5

set dclpath = . .. C:/Cadence/SPB_16.6/share/pcb/pcb_lib C:/Cadence/SPB_16.6/share/pcb/allegrolib

set devpath = D:\Allegro_LIB\Allegro_LIB\

set dfaauditpath = . C:/Cadence/SPB_16.6/share/local/pcb/assembly C:/Cadence/SPB_16.6/share/pcb/assembly

set dfacnspath = . dfa .. ../dfa C:/Cadence/SPB_16.6/share/local/pcb/dfa

set display_backingstore = on

set display_nohilitefont =

set display_norepair = rats

set display_shapefill = 4

set display_shapefill_analysis = 2

set dpm_dbext = dpm

set dps_dbext = dps

set drawing_4mils =

set drc_diff_pair_overide = 0

set envpath = C:/Users/chenmaojie/AppData/Roaming/SPB_Data/pcbenv C:/Cadence/SPB_16.6/share/pcb/text

set ext_artwork = art

set ext_drill = drl

set film_nosort =

set formpath = . C:/Cadence/SPB_16.6/share/local/pcb/forms C:/Cadence/SPB_16.6/share/pcb/text/forms

set fp_no_host_check = NO

set global = C:/Cadence/SPB_16.6/share/pcb/text

set globalpath = . C:/Cadence/SPB_16.6/share/pcb/text

set helppath = . C:/Cadence/SPB_16.6/share/pcb/help C:/Cadence/SPB_16.6/share/pcb/text/help

set home = C:/Users/chenmaojie/AppData/Roaming/SPB_Data

set homedrive = C:

set homepath = \Users\chenmaojie

set ignore_popup_action =

set imagepath = . C:/Cadence/SPB_16.6/share/pcb/examples/image

set kanjifont1 = kanjifont1

set kanjifont2 = kanjifont2

set kanjifontpath = . C:/Cadence/SPB_16.6/share/pcb/text/fonts/kanji

set ldfpath = .

set localappdata = C:\Users\chenmaojie\AppData\Local

set localenv = C:/Users/chenmaojie/AppData/Roaming/SPB_Data/pcbenv

set localpath = . C:/Users/chenmaojie/AppData/Roaming/SPB_Data/pcbenv C:/Cadence/SPB_16.6/share/local/pcb . C:/Cadence/SPB_16.6/share/pcb/text

set logonserver = \\CHMJ

set materialpath = . C:/Users/chenmaojie/AppData/Roaming/SPB_Data/pcbenv C:/Cadence/SPB_16.6/share/local/pcb C:/Cadence/SPB_16.6/share/pcb/text

set mcm_dbext = mcm

set menuload = allegro

set menupath = . C:/Cadence/SPB_16.6/share/local/pcb/menus C:/Cadence/SPB_16.6/share/pcb/text/cuimenus

set module = TR5_A0.brd

set modulepath = . C:/Cadence/SPB_16.6/share/local/pcb/modules

set ncdpath = . .. C:/Cadence/SPB_16.6/share/local/pcb/nclegend C:/Cadence/SPB_16.6/share/pcb/text/nclegend

set noshow_current_selections =

set number_of_processors = 4

set oa_plugin_path = C:\Cadence\SPB_16.6\Share\oaPlugIns

set os = Windows_NT

set padpath = E:\layout working\SPO2 WITH MFI\SPO2 LIB\ D:\ALLEGRO\ E:\LAYOUT WORKING\PACKAGE\1394\ E:\LAYOUT WORKING\PACKAGE\11.10\

set path = C:\MentorGraphics\Allegro Export ODB++\nv\bin C:\Program Files (x86)\NVIDIA Corporation\PhysX\Common C:\Windows\system32 C:\Windows C:\Windows\System32\Wbem C:\Windows\System32\WindowsPowerShell\v1.0\ C:\Program Files (x86)\WinMerge C:\Program Files\TortoiseSVN\bin C:\Program Files (x86)\Skype\Phone\ C:\Cadence\SPB_16.6\openaccess\bin\win32\opt C:\Cadence\SPB_16.6\tools\capture C:\Cadence\SPB_16.6\tools\pspice C:\Cadence\SPB_16.6\tools\specctra\bin C:\Cadence\SPB_16.6\tools\fet\bin C:\Cadence\SPB_16.6\tools\libutil\bin C:\Cadence\SPB_16.6\tools\bin C:\Cadence\SPB_16.6\tools\pcb\bin

set pathext = .COM .EXE .BAT .CMD .VBS .VBE .JS .JSE .WSF .WSH .MSC

set pcb_cursor = cross

set pcell_lib_path = C:/Cadence/SPB_16.6/share/local/pcb/../../rfsip/sip_pcells . sip_pcells .. ../sip_pcells

set pdfpath = . C:/Cadence/SPB_16.6/share/pcb/help/pdf

set pm_cmdmap = allegro

set prfeditpath = . configure/prfedit C:/Users/chenmaojie/AppData/Roaming/SPB_Data/pcbenv/configure/prfedit C:/Cadence/SPB_16.6/share/pcb/configure/prfedit

set processor_architecture = x86

set processor_architew6432 = AMD64

set processor_identifier = Intel64 Family 6 Model 37 Stepping 5, GenuineIntel

set processor_level = 6

set processor_revision = 2505

set programdata = C:\ProgramData

set programfiles = C:\Program Files (x86)

set programfiles(x86) = C:\Program Files (x86)

set programw6432 = C:\Program Files

set psmodulepath = C:\Windows\system32\WindowsPowerShell\v1.0\Modules\

set psmpath = E:\layout working\SPO2 WITH MFI\SPO2 LIB\ D:\ALLEGRO\ E:\LAYOUT WORKING\PACKAGE\1394\ E:\layout working\package\11.10\

set public = C:\Users\Public

set roaminc = 96

set scfpath = . scfs .. ../scfs

set scriptpath = . C:/Cadence/SPB_16.6/share/local/pcb/scripts C:/Cadence/SPB_16.6/share/pcb/text/script

set sessionname = Console

set si_model_path = .

set signal_install_dir = C:/Cadence/SPB_16.6/share/pcb/signal

set signal_optlib_dir = C:/Cadence/SPB_16.6/share/pcb/signal/optlib

set signoisepath = . C:/Users/chenmaojie/AppData/Roaming/SPB_Data/pcbenv C:/Cadence/SPB_16.6/share/local/pcb/signal C:/Cadence/SPB_16.6/share/pcb/signal C:/Cadence/SPB_16.6/share/pcb/signal/optlib C:/Cadence/SPB_16.6/share/pcb/text

set sip_dbext = sip

set slide_arcs =

set sproutepath = C:/Cadence/SPB_16.6/share/pcb/configure/sproute

set subclass = OUTLINE

set systemdrive = C:

set systemroot = C:\Windows

set techpath = . C:/Cadence/SPB_16.6/share/local/pcb/tech C:/Cadence/SPB_16.6/share/pcb/text/tech

set telenv = C:/Cadence/SPB_16.6/share/pcb/text/env

set temp = C:\Users\CHENMA~1\AppData\Local\Temp

set textpath = . C:/Cadence/SPB_16.6/share/local/pcb/extracta C:/Cadence/SPB_16.6/share/pcb/text/views

set tilepath = . C:/Cadence/SPB_16.6/share/local/pcb/modules

set tmp = C:\Users\CHENMA~1\AppData\Local\Temp

set topfilelib = C:/Cadence/SPB_16.6/share/pcb/pcb_lib/templates C:/Cadence/SPB_16.6/share/pcb/allegrolib/templates

set topology_template_path = . templates .. ../templates C:/Cadence/SPB_16.6/share/local/pcb/topology C:/Cadence/SPB_16.6/share/pcb/pcb_lib/templates C:/Cadence/SPB_16.6/share/pcb/allegrolib/templates

set units = C:/Cadence/SPB_16.6/share/pcb/text/units.dat

set userdomain = chmj

set username = chenmaojie

set userprofile = C:\Users\chenmaojie

set vectorfontpath = . C:/Cadence/SPB_16.6/share/pcb/text

set viewlog = E:/working/tr5/signoise.log

set viewpath = . C:/Cadence/SPB_16.6/share/local/pcb/views

set wbpath = . C:/Cadence/SPB_16.6/share/local/pcb/wbtiers

set windir = C:\Windows

set windows_tracing_flags = 3

set windows_tracing_logfile = C:\BVTBin\Tests\installpackage\csilogfile.log

set wint =

set wirebond_hud_update_frequency = 25

set wirebond_suppress_bondwire_drcs =

set wizard_template_path = . .. C:/Cadence/SPB_16.6/share/pcb/pcb_lib/symbols/template

set xtalk_table_path = . xtalk_tables .. ../xtalk_tables C:/Cadence/SPB_16.6/share/local/pcb/xtalk C:/Cadence/SPB_16.6/share/pcb/pcb_lib/xtalk_tables

set __compat_layer = DisableThemes

set _allegro_adv_optimize =

set _allegro_aibt_built_in =

set _allegro_cns_regions_ok = 1

set _allegro_cstm_nclegend_ok = 1

set _allegro_diffpair_ok = 1

set _allegro_diffpair_static_ok = 1

set _allegro_ecsetflatten = 1

set _allegro_elec_cns_ok = 1

set _allegro_electrical_checks = 1

set _allegro_gre_all = 1

set _allegro_gre_ifd = 1

set _allegro_gre_view = 1

set _allegro_group_route = 1

set _allegro_ibd_all = 1

set _allegro_ibd_view = 1

set _allegro_mini_ok = 1

set _allegro_pcb_gxl =

set _allegro_ratt_ok = 1

set _module = TR5_A0.brd

set _module_base = TR5_A0

set _program = allegro

这个是我allegro 的设置

看下你环境变量里temp及tmp路径在哪里,你把temp及tmp文件清空一下就好了,以前遇到过。

还是不行啊

一点一点来排查吧。

建议不要把路径设置到有空格的目录,例如padpath的路径。

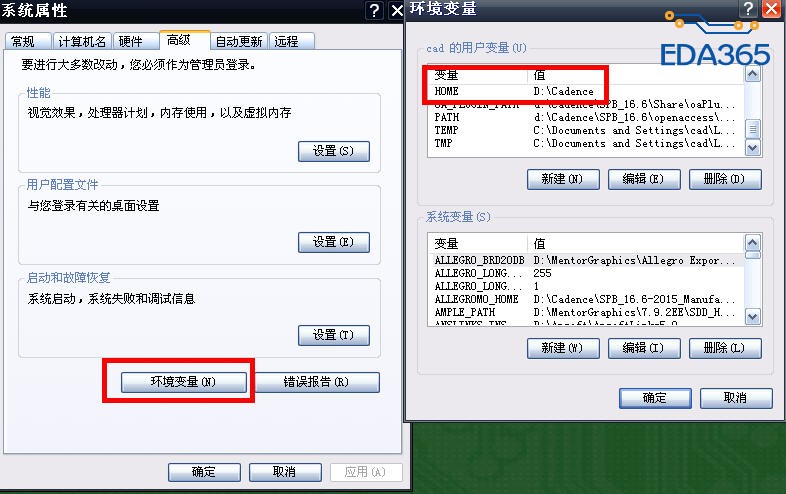

看情形,你的Home路径好像也没设置,用的是系统默认的,建议改一下。

si_model_path的路径只有一个点?我的是这样的:

set si_model_path = . D:/Cadence/SPB_16.6/share/local/pcb/signal D:/Cadence/SPB_16.6/share/pcb/signal

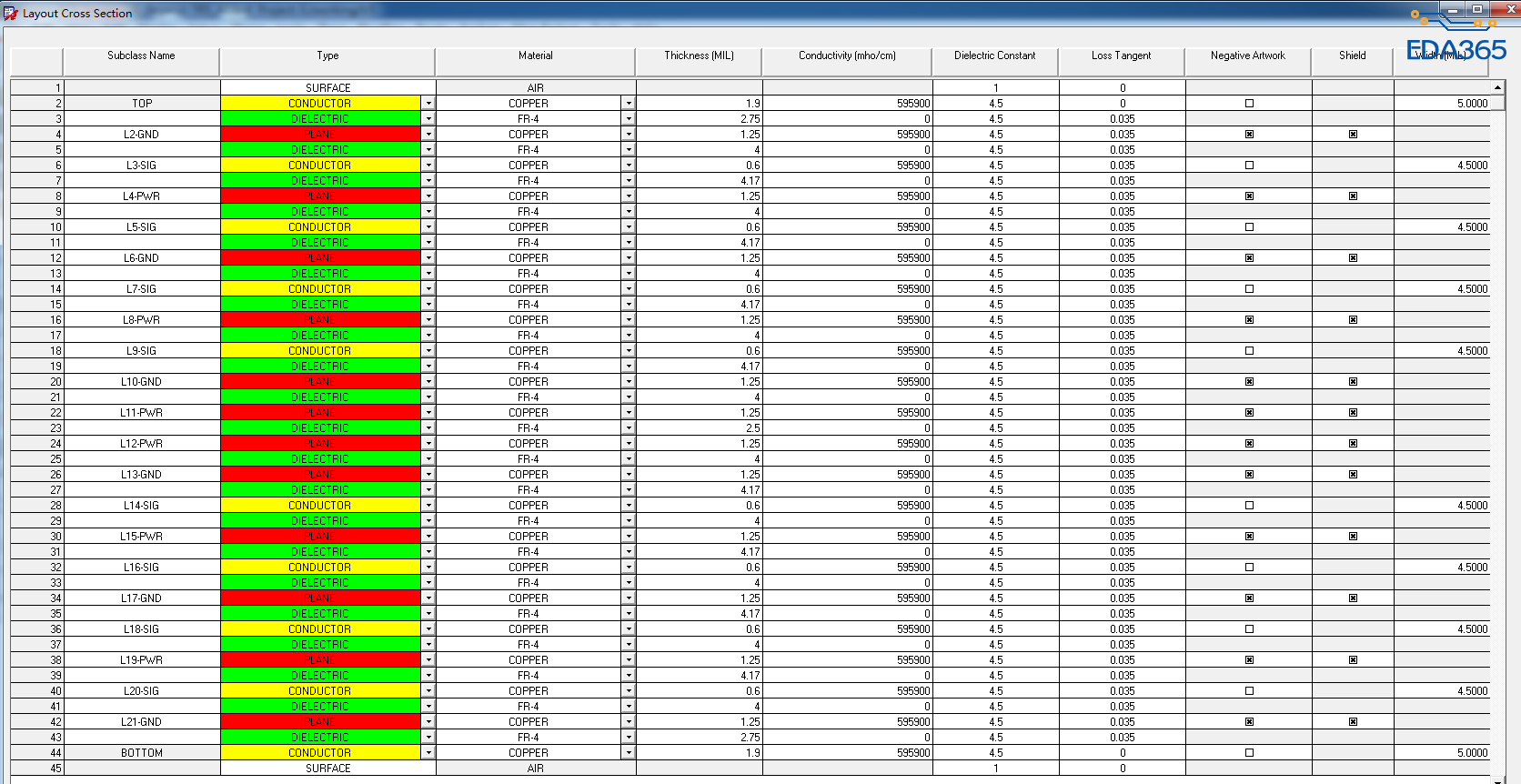

你的板子叠层设置界面也截个图出来看下吧。

我从来都没有设置过home路径 不知道怎么设置

求救

xp系统的设置方法,供参考

哎

我好蛋疼

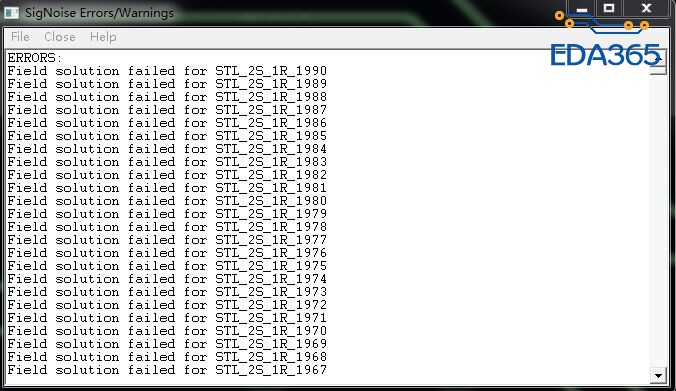

SigNoise Errors/Warnings

Started by xrwright on 1 Dec 2013 10:05 AM. Topic has 1 replies and 548 views.

Last post on 2 Dec 2013 5:06 AM by Dennis Nagle.

Hi,

All of the sudden whenever I open Cross-section and try to change Coupling Type or go to do a diff route on this particular board, an error dialog box named "SigNoise Errors/Warnings" pops up which shows this list:

WARNINGS:

Iml model STL_2S_1R_TRACE6 is duplicated 2 times in libraries

interconn.iml ..\..\..\..\Cadence\SPB_16.6\share\pcb\signal\cds_interconn.iml.

Iml model STL_2S_1R_TRACE48 is duplicated 2 times in libraries

interconn.iml ..\..\..\..\Cadence\SPB_16.6\share\pcb\signal\cds_interconn.iml.

Iml model STL_2S_1R_TRACE36 is duplicated 2 times in libraries

interconn.iml ..\..\..\..\Cadence\SPB_16.6\share\pcb\signal\cds_interconn.iml.

Iml model STL_2S_1R_TRACE24 is duplicated 2 times in libraries

interconn.iml ..\..\..\..\Cadence\SPB_16.6\share\pcb\signal\cds_interconn.iml.

Iml model STL_2S_1R_TRACE16 is duplicated 2 times in libraries

interconn.iml ..\..\..\..\Cadence\SPB_16.6\share\pcb\signal\cds_interconn.iml.

Iml model STL_2S_1R_CPW76 is duplicated 2 times in libraries

interconn.iml ..\..\..\..\Cadence\SPB_16.6\share\pcb\signal\cds

......

......

It continues for a lot more lines showing different models. These errors are also replicated in the dialog area at the bottom of the screen.

It's only happening for this board and no others.

Anyone know how I can correct this? Thanks!

Robert

xrwright xrwright

1 Dec 2013 10:05 AM Reply

1 Reply

Dennis Nagle Dennis Nagle

2 Dec 2013 5:06 AM

Robert,

The easy solution is to delete your local copy of interconn.iml - this file should be located in your working directory where the .brd is. This file is just a local cache of field solver output. Each of those "STL_2S_1R ...." entries is a coupled trace model which contains the differential impedance.

The bigger questions are what your desires are at this stage of the design (and/or whether someone else like the SI engineer is using the same directory). If you don't need or want to see differential impedance calculated in the Layout Cross Section dialog, then diable the checkbox in the lower right hand corner of the dialog for "Show Diff Impedance". This is what is forcing the field solver to be called. You also may or may not want to disable the imedance DRC if you are also seeing these messages generated when routing a diff pair.

The messages also indicate that algorithmic models are enabled and that you are using the full wave solver. If you don't understand what these are and want to fully understand the implications, feel free to contact me offline.

Regards,

-Dennis Nagle

Cadence

Reply

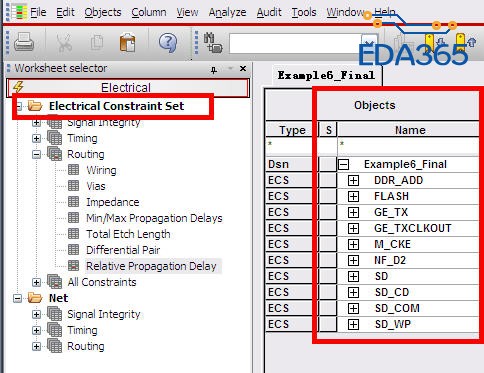

看看是不是有等长参考模型,如果有,再全部重新提取生成一遍。

确实蛋疼...我感觉是文件的问题....去别人机器试试,如果都有上个文件呗.

最后重新装系统,就好了