- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请问allegro网表中怎么添加高度信息?

'AXT524124' ! 'AXT524124' ; J2

'OK_21M040_04' ! 'OK_21M040_04' ; J1

$NETS

'CAM_I2C_SDA' ; J1.26 J2.7

'CAM_I2C_SCL' ; J1.27 J2.6

'MCAM_RST_N' ; J1.28 J2.9

'MCAM_PWDN' ; J1.9 J2.10

'CAM0_MCLK' ; J1.7 J2.8

'GND' ; J1.3 J1.6 J1.8 J1.12 J1.17,

J1.20 J1.29 J1.32 J1.35 J1.38,

J1.24,

J2.26 J2.25 J2.22 J2.19 J2.16,

J2.13 J2.28 J2.27 J2.5

$END

可以这样加么?

可以的,有的公司用的别的原理图软件,只能通过网表传递信息

你不如直接把零件高度放在Value里

怎么做?最好不要在封装里添加,因为同一个封装对应不同器件时,高度可能不一样

线路里 每一颗零件都有Value 么 在Value里加上H=XX 不就好了

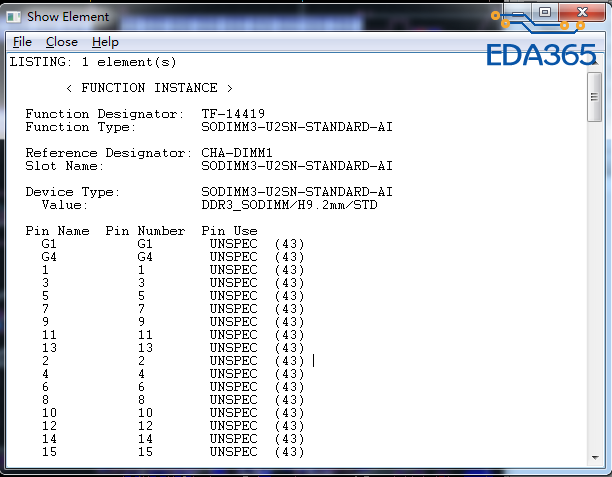

例如 SODIMM 我在查Functions 的时候会显示这个

貌似高度信息不是在网标中体现吧

举例:

'AXT524124' ! 'AXT524124' ; J2

改为

'AXT524124' ! 'AXT524124 H=3.0mm' ; J2

只能通过这样的方式。

这样不行啊,报错误:

$PACKAGES

'TP_DBG_1P27X10' ! 'TP_DBG_1P27X10 H=3.0mm' ; J1

^

ERROR(SPMHNI-67): Cannot find device file for 'TP_DBG_1P27X10 H=3.0MM'.

有两个问题:

1、我不是用的Cadence的原理图设计软件,不一定有添加value的地方。不过这个可以通过工具批量改网表实现。就不算问题了。

2、您这种方法可以输出带高度信息的文件给结构设计吗?比如输出emn文件给proe导入设计。

谢谢!

说了半天不还是封装里加那个么,那个value里加的就是基本没啥用还影响别人看value值.

那就改为

'AXT524124' ! 'AXT524124!'H=3.0mm' ; J2

除非改封装,否则无法输出高度信息给结构核对。

封装不改 线路也不改 那么你板子上直接标注

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:Thieving功能是干什么用的?

下一篇:自动放过孔时,已设置same net spacing中via和SMD pin为5mil,为何还会打在pin上