- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

16.6中如何按照网络手动添加via?shape的安全间距修改了为何不能自动更新?

有时候希望不走线添加过孔,例如选择电源地或者其他的信号网络,先添加过孔进行对齐处理后连线。不知道在16.6如果操作,或者有没有类似的skill?

shape的安全间距修改了为何不能自动更新?

在规则约束里面更新shape到smd的安全间距后,原先的shape就是变成一个整体的shape,把整个部分覆盖住,也不见DRC错误显示(例如shape原先的网络是GND)

不能自动更新?是不是只能手动选择点击 删除孤岛的方式更新?

或者像类似这样的情况,如果约束规则改了是不是会存在有些不能马上更新的情况?如何判断(现在只是简单随意修改了shape到via或者SMD的安全间距)

扇出的时候 能分别选择不同的via吗?例如电源地我选择比较大的via,信号 选择比较小的via

例如电源或者地指定的via类型有几种

如何在扇出的时候选择指定正确的via自动扇出?

发表于 2015-8-12 16:23 | 只看该作者 |倒序浏览 |阅读模式

16.6中如何按照网络手动添加via?

有时候希望不走线添加过孔,例如选择电源地或者其他的信号网络,先添加过孔进行对齐处理后连线。不知道在16.6如果操作,或者有没有类似的skill?7 l* w9 q3 V, j$ M" C& Z3 P7 \

这个有skill 吧 ?

在或者用 copy 命令不就可以了 ?

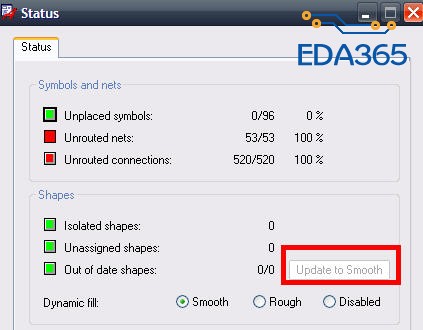

修改约束规则后,要到Display-Status更新铜箔。

在哪里有这个skill?

不能自己自动跟新?

1:你可以直接添加via之後連線賦net

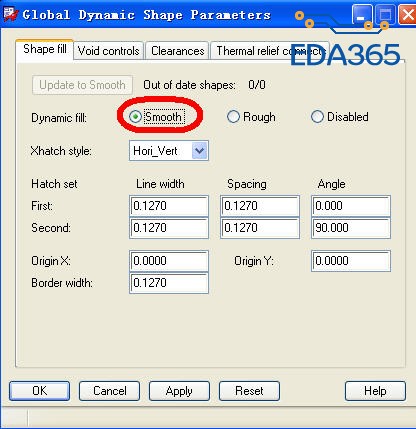

1:可以先打via,之後連線賦net 2,修改約束規則之後,必須去更新銅箔 3,走線狀態下option下面可以選擇使用哪個via,前提是板子設置好可用via(規則里設置) 4

直接先打孔怎么操作?默认都是拉线出来 打孔

我希望点击对应网络 连续打孔

走線狀態下雙擊左鍵。即可打孔。

這種孔如果沒有打在走線上或者shape上,net屬性為dummy net(無net屬性),可以直接把有net的走線拉到這種via給其賦net屬性。

勾选SHAPE/ GLOBAL DYNAMIC PARAMS...下的这个选项;

看来只能这样了 无法自动更新哦

謝謝分享

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:ALLEGRO认为的封装非法字符有哪些?

下一篇:关于封装制作的问题