- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于线和线的DRC

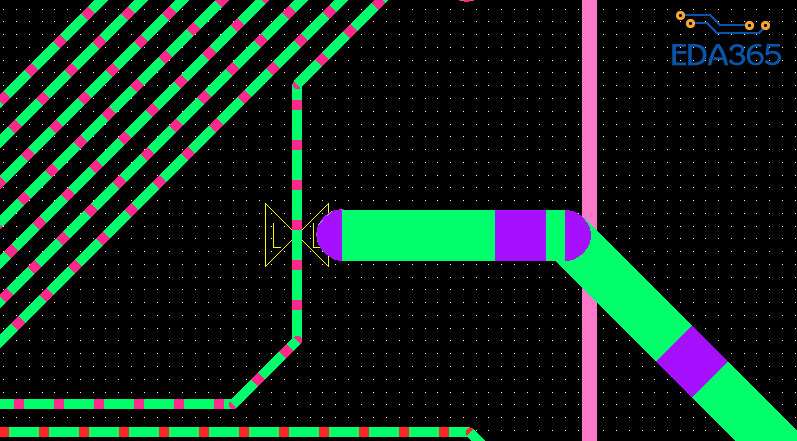

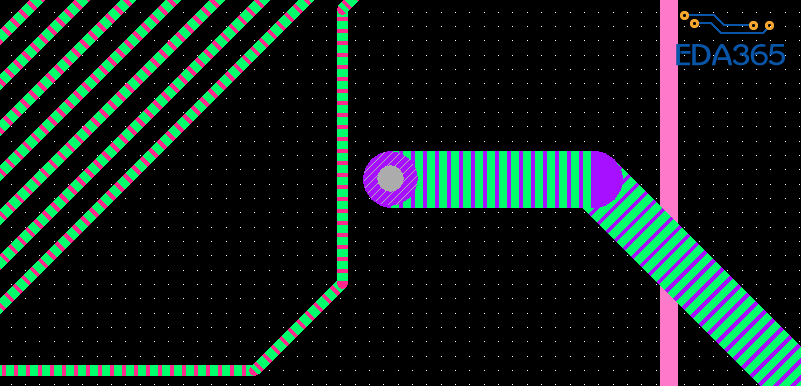

15版本当出现这种情况会show出DRC

16版本这种情况却show不出DRC

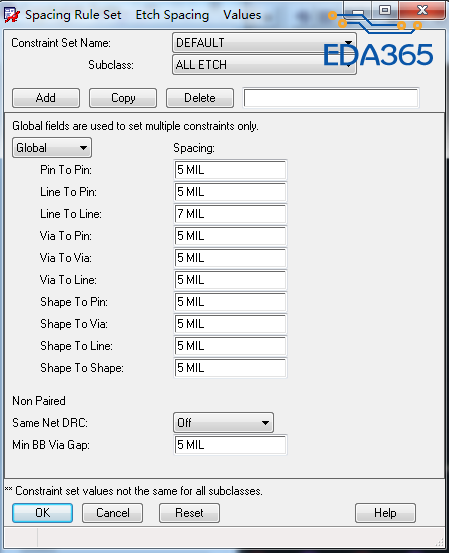

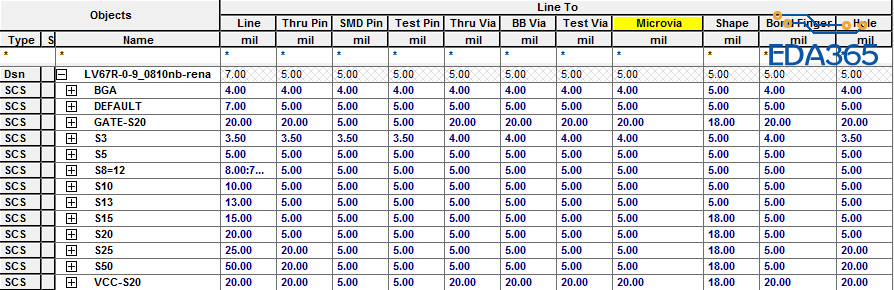

把设置的规则贴出来看下。

应该是这两个

15版本会显示线和线的DRC 16版本如果线打了VIA 就变成 线和VIA的DRC了

用i查询命令查一下15版的DRC信息,发上来看看。

16版中,这两根线分别是指定的什么间距约束规则?

是否这两个线在不同的bus中

15版本的DRC 是 线和线 没保持7mil 16版本这样是show不出DRC,但是把Via DEL 就能show出DRC,所以我得出的结论是16版本当线下孔后线和线的规则被线和Via的规则所取代.这样就没法检查下Via的线与别的线保持间距. (主要指的是图片上的这种情况)

这两个图是同一个 一个用15打开 一个16打开的 设置也是一样的 但是同个区域 15能show出DRC 16不能 但是正版的16就能show出DRC

将16x DRC show element 看具体出错在哪个约束下,再去针对性找问题,16x版本更严谨

也许只是正版和盗版的区别 因为 同样正版不会出现这种问题

话说,我目前还没遇到此类情况,软件也是盗版的

可能也是为了让线宽不要超过via的pad宽度,毕竟线再宽,via过不了那么多电流也是白搭

你试试看 设置线和线保持7MIL 线和孔保持5MIL 然后 你拉个20MIL粗的线打个20d10的孔 然后再拉根线过去 跟VIA保持5MIL 看看线和VIA里的线没有保持7mil 会不会出DRC 我这边15会出 16直接无视了

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:Placement->componts by redes里为什么没有器件啊?!

下一篇:mechanical symbol 如何编号?