- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请问这个长度怎么设定?

录入:edatop.com 点击:

看到layout guideline写,时钟线与DQS的关系是, DQS MIN LENGTH=CLOCK-2500 , MAX LENGTH =CLOCK+1500 .

看来数学没学好。

按layout guideline要求,公式应该是这样的:

CLOCK-2500<DQS<CLOCK+1500

变换一下:

(CLOCK-500)-2000<DQS<(CLOCK-500)+2000

这岂不就是DQS=(CLOCK-500)+/-2000

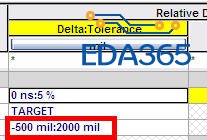

把公式变换一下,理解等长设置中Delta的作用。假设以时钟线为基准,参考下图:

-500 :2000 是怎么算出来的?

个人感觉应该是-2500:1500吧。

这个layout guide的规则放的相当宽了,一般等长做完都会在这个范围之内。到时候自己检查下有没有在这个范围里面就OK了。

再请教,这个要怎么设?

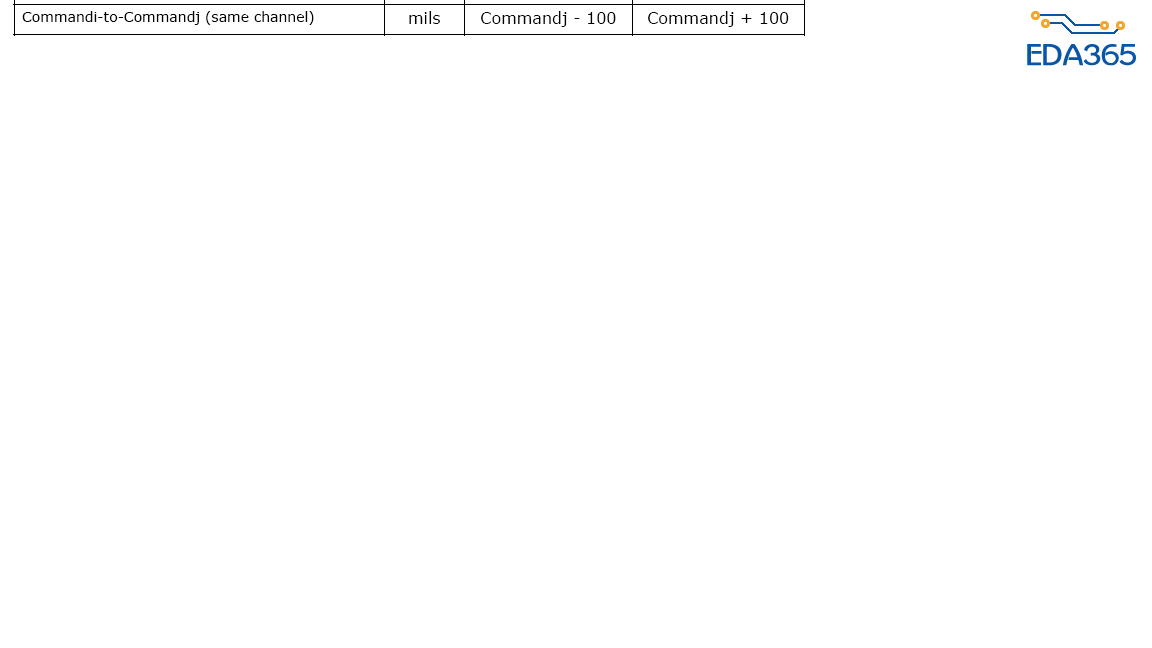

i j是什么意思?

应该是指不同信号名,没有备注吗?

-(2500+1500)/2:(2500-1500)/2

这应该是ddr2了 ddr3的dqs和clk好像没等长关系了吧.

不知道ddr几,随便翻到了,就看看.

同组command 最长最短误差不超过100mil

谢谢,还应为是200mil呢?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:求助USB原理图

下一篇:上司让从candence转到protel99se