- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Allegro设置BGA区域规则的疑惑

录入:edatop.com 点击:

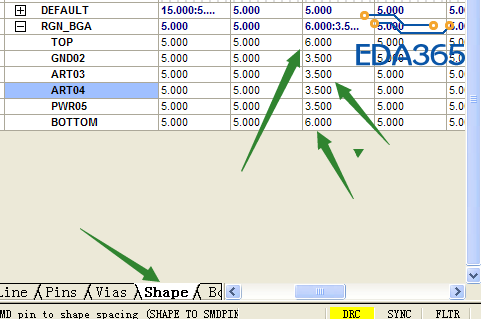

Allegro设置BGA区域规则时,设置了各层的shape到via的距离分别为TOP/BOTTOM为6MIL;L3/L4为3.5MIL,REGON的层属性是ALL,为什么实际铺铜后,所有层都按照3.5mil间距铺铜呢?

是不是铜箔参数中的避让设置是3.5mil?建议上传文件,以便准确定位问题。

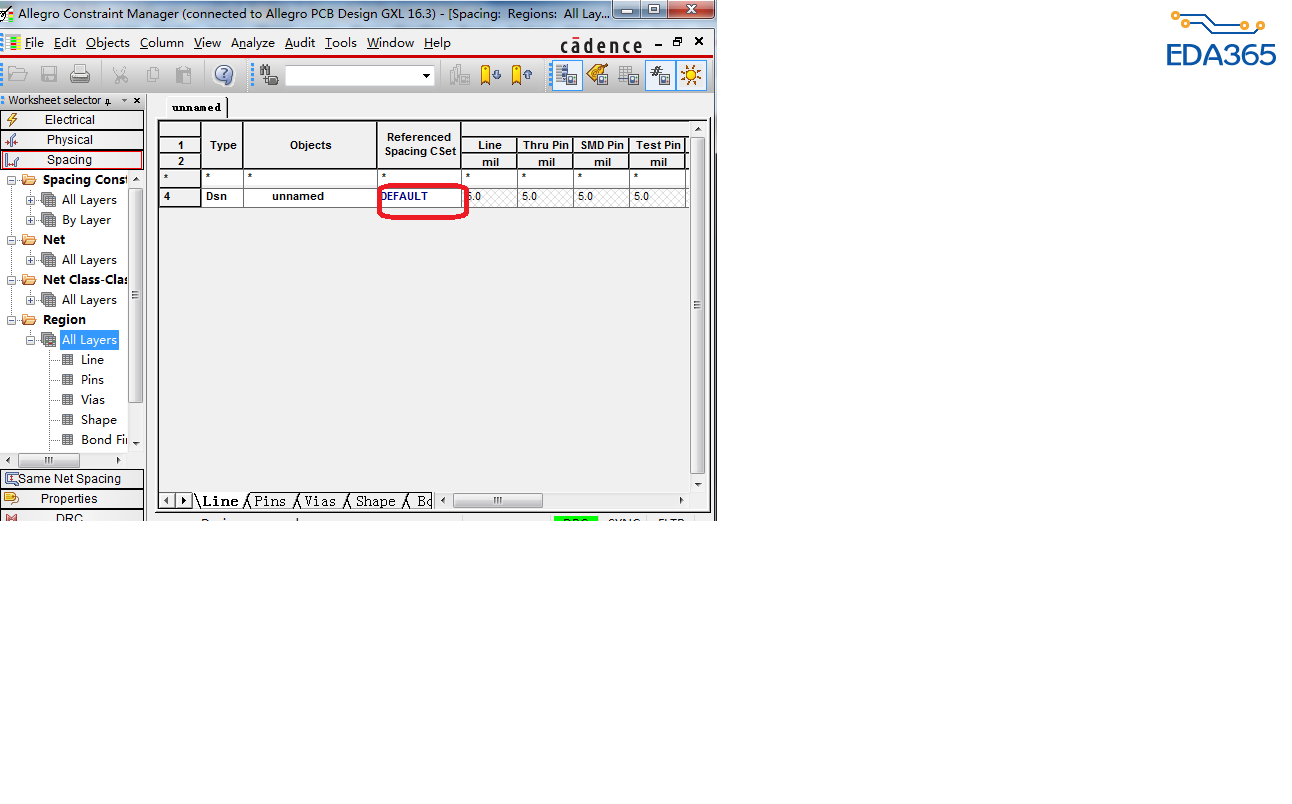

一般有两种可能:

1是如下图,红圈里面是否把你设置好的BGA规则给吃进来

2是打开PCB中甚至的BGA区域,用属性的方式show一下你这个区域规则是不是用你所设置的region name.

应该是区域规则