- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于导网表的问题

生成网表,确定是OK的

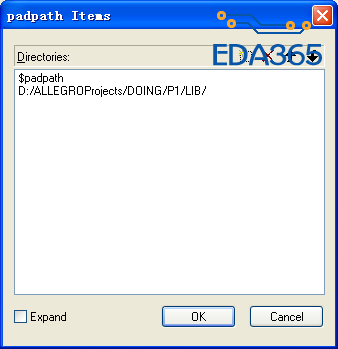

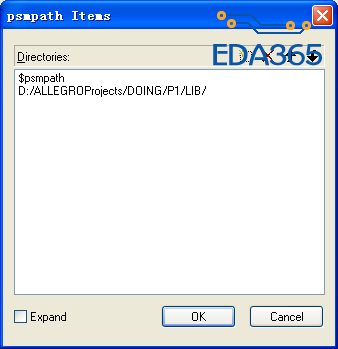

库路径设置也确定OK的

PCB工作区域确定也是OK的,可硬是没有一个元件出来,哪怕是电阻电容都没有,试了N遍,换了一台电脑,仍旧不行,试过以前的项目,都是OK的,

真无奈~~~~╮(╯▽╰)╭

下面是导网表后的信息,

(---------------------------------------------------------------------)( )( Allegro Netrev Import Logic )( )( Drawing : P1.brd )( Software Version : 16.6P004 )( Date/Time : Fri Nov 13 19:45:12 2009 )( )(---------------------------------------------------------------------)------ Directives ------RIPUP_ETCH FALSE;RIPUP_DELETE_FIRST_SEGMENT FALSE;RIPUP_RETAIN_BONDWIRE FALSE;RIPUP_SYMBOLS ALWAYS;Missing symbol has error FALSE;SCHEMATIC_DIRECTORY 'D:/ALLEGROProjects/DOING/P1/allegro';BOARD_DIRECTORY '';OLD_BOARD_NAME 'P1.brd';NEW_BOARD_NAME 'P1.brd';CmdLine: netrev -$ -i D:/ALLEGROProjects/DOING/P1/allegro -y 1 D:/ALLEGROProjects/DOING/P1/#Taaaads05108.tmp------ Preparing to read pst files ------Starting to read D:/ALLEGROProjects/DOING/P1/allegro/pstchip.dat Finished reading D:/ALLEGROProjects/DOING/P1/allegro/pstchip.dat (00:00:00.06)Starting to read D:/ALLEGROProjects/DOING/P1/allegro/pstxprt.dat Finished reading D:/ALLEGROProjects/DOING/P1/allegro/pstxprt.dat (00:00:00.01)Starting to read D:/ALLEGROProjects/DOING/P1/allegro/pstxnet.dat Finished reading D:/ALLEGROProjects/DOING/P1/allegro/pstxnet.dat (00:00:00.01)------ Oversights/Warnings/Errors ------#1 ERROR(SPMHNI-176): Device library error detected.ERROR(SPMHNI-164): Problems with device 'AUR9707_0_WDFN-33-12_AUR9707'. JEDEC_TYPE property 'WDFN-3×3-12' is illegal: 'Package name has invalid characters or is too long.'.ERROR(SPMHNI-170): Device 'AUR9707_0_WDFN-33-12_AUR9707' has library errors. Unable to transfer to Allegro.------ Library Paths ------MODULEPATH = . C:/Cadence/SPB_16.6/share/local/pcb/modules PSMPATH = D:/ALLEGROProjects/DOING/P1/LIB/ PADPATH = D:/ALLEGROPROJECTS/DOING/P1/LIB/ ------ Summary Statistics ------#2 Run stopped because errors were detectednetrev run on Nov 13 19:45:12 2009 DESIGN NAME : 'VL100_APP_LIKE_VGA_SCH_0904A' PACKAGING ON Sep 10 2012 04:46:09 COMPILE 'logic' CHECK_PIN_NAMES OFF CROSS_REFERENCE OFF FEEDBACK OFF INCREMENTAL OFF INTERFACE_TYPE PHYSICAL MAX_ERRORS 500 MERGE_MINIMUM 5 NET_NAME_CHARS '#%&()*+-./:=>?@[]^_`|' NET_NAME_LENGTH 24 OVERSIGHTS ON REPLACE_CHECK OFF SINGLE_NODE_NETS ON SPLIT_MINIMUM 0 SUPPRESS 20 WARNINGS ON 2 errors detected No oversight detected No warning detectedcpu time 0:00:31elapsed time 0:00:00

二个错误都很明显的错误 AUR9707_0_WDFN-33-12_AUR9707 检查这个就行了

Problems with device 'AUR9707_0_WDFN-33-12_AUR9707'. JEDEC_TYPE property 'WDFN-3×3-12' is illegal: 'Package name has invalid characters or is too long.'.ERROR(SPMHNI-170): Device 'AUR9707_0_WDFN-33-12_AUR9707' has library errors. Unable to transfer to Allegro.

你看这些错误提示,可以先在原理图中把相关的元件删除,再导入一下试试,看有问题没,先定位一下问题,如果依然出错,再看出错提示,如果没有,那么就去修改提到错误的元件就行了,希望能帮到你

封装名有非法字符 WDFN-3×3-12,把 乘号 修改为 X , WDFN-3X3-12

都提示错误,有非法字符

那为什么我一个元件都导不进来呢?

这个思路不错,学习了

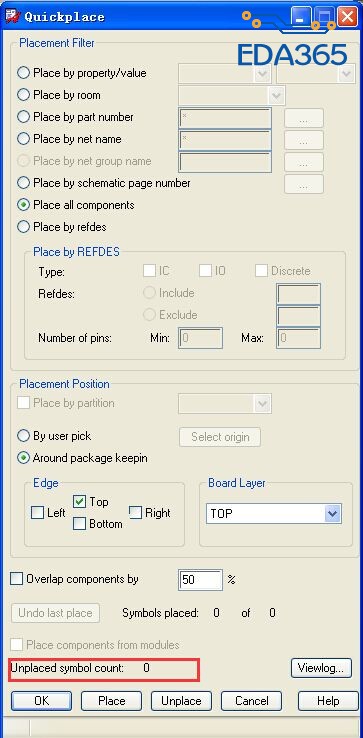

倒不进来是因为没有板框,或者零件库路径没有设好.

------#2 Run stopped because errors were detectednetrev ,这才是你一个元件都导不进来的真正原因。已经告诉你run stopped , 说明网表根本就没起作用,何来元器件? 你的封装名有非法字符“-”,封装名不能用中杠线,改用下划短线'_"(shift + 短横线)

是啊 多看看提示

感谢解答,我重现换了一份原理图,然后把封装名整理了下就搞定了

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:关于allegro生成的元件的位置图(pdf)中搜索元件位置问题

下一篇:ALLEGRO artwork 出不了光绘点击没有反应