- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

allegro针对BGA布线能不能按照内侧外侧扇出走线?

就是在扇出过孔以后,规划内层布线,能不能指定层自动走出BGA所在区域?

研究一下FSP功能吧,有什么心得也跟大家分享一下。

我在研究FSP,但是也看了文档表述 FSP只能作为初级布局;未考虑走线因素

如果以后的版本可以直接有扇出走线因素可以添加进去的话,优化的结果会更好一些

我现在用的也不是很熟悉

我也是先在FSP里面进行预优化,然后导入进allegro里面,还需要手动添加bundle(FSP里面的group也不能自动加载上,如果能就方便了多,不知道以后能不能改进这个,将group自动变成bundle?)

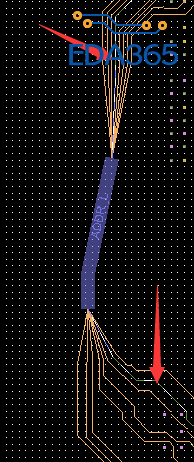

在bundle规划出线的时候感觉 结果有时候还不是很好

有时候需要自己手动拉出线 而且要把两边的线拉近的时候 使用自动FSP交换管脚才能得到相当好的结果,有时候也存在交叉线(明显的我已经将两边的线拉顺了,但是发现有的可以顺有的没有顺,不是很清楚在操作上还有那些经验可以参考?)

在对bundle特性约束的时候,我就指定它只能布线在那个层,然后选择minDRC(不知道这个选择对不对),其他的好像也没啥可以选择的

bundle的自动brake out both ends感觉也不是很好,有时候出来的结果都是乱七八糟的饶线

所以还是希望BGA除了自动扇出via后,能指定层进行自动扇出一段走线可能在规划的时候效果更好一些,也可以规划布线在哪些比较好

这方面经验不足,不知道大家在用allegro规划布线与布局的时候有哪些经验?

看过一些简单的bundle的介绍

但是还是有点摸不清头脑

例如我在两边的器件只拉出一小段走线

自动优化的时候发现总找不到最佳顺的方式,存在交叉(目标一侧的IO按理说是可以任意交换,如果器件的一侧规划处最少通孔的走线,如果能自动优化走顺的话就是最好的结果)

或者如果FSP里面直接支持bundle规划就更好了

bundle有无好的导入导出与编辑的方法?默认在规则管理器里面好像导不出来,导出的规则好像导入的时候不能把bundle导入进去?

有时候拉出来的bundle 在优化的总是存在交叉,不知道怎么才能正确交换

请问什么是FSP 功能,我现在正在寻求BGA扇出,怎么扇出后各引脚引线都自动拉出来