- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何设置顶层和底层flash挖空大小

录入:edatop.com 点击:

见图。这是我的电源插座,为了焊接可靠,我想把GND引脚的flash扣挖部分也设置成20MILL宽,但是不知道在哪里设置啊?默认的只有3mil不到。

GND的flash挖空太小

我觉得你这个 只是需要那些避让 就点击那些pin 这样对应单独需要要求的比较好用!不过小编应该是要整板的!所以还是去规则那里修改下!不过你这种方法我就是很喜欢用!特别是螺丝孔避让就很好用!

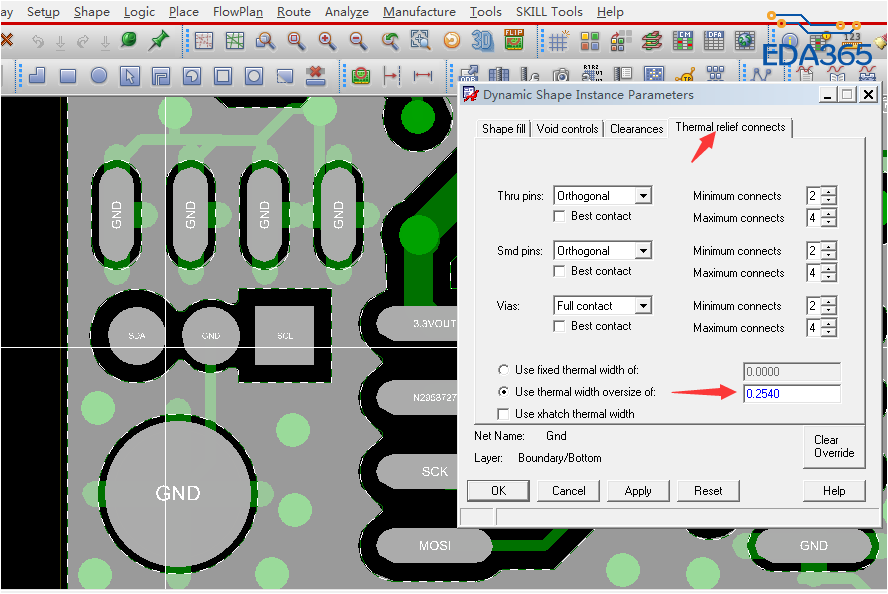

可以试一下,选择到铺的铜,打开“参数:

谢谢,下来试试

不行,这个位置改的是十字花宽窄

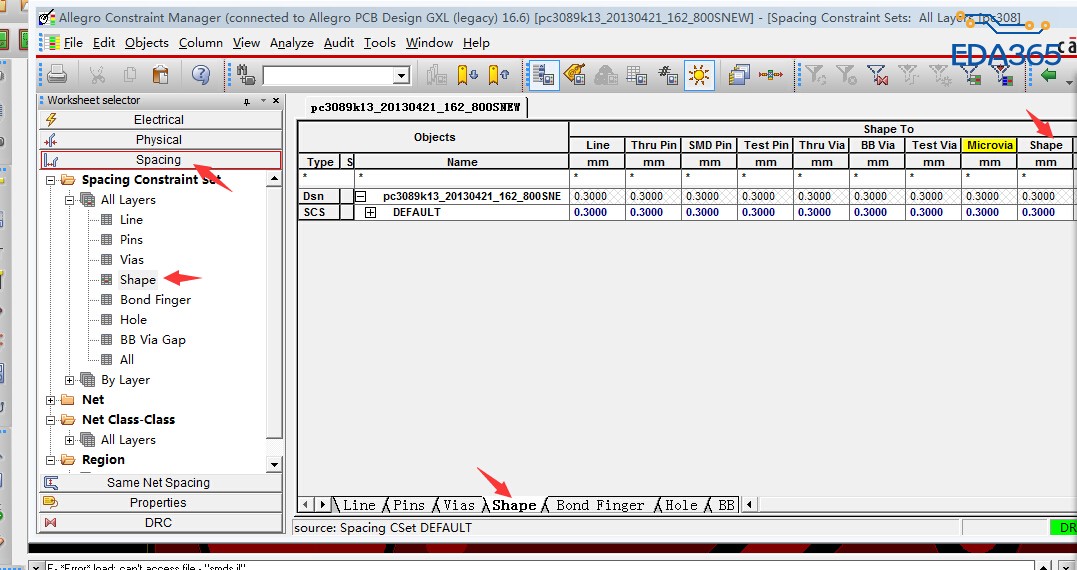

应该是去约束管理器设置same net spacing吧

不好意思,还是要在约束规则内把SHAPE的间距改大成0.3mm.

不好意思,还是要在约束规则内把SHAPE的间距改大成0.3mm.

没看懂呢,顶层的flash...这个概念有点厉害啊~~

设置pin的属性,dyn_clearance_oversize填入合适的值使其避让。

这个说法是不科学,但能明白意思就行了啊。我说的就是顶层GND与铜皮之间扣掉的部分

非常感谢各位热心的网友,特别是“JIMDENG”,还给耐心截图!我下来再试试

试了这个方法,确实管用。用于螺孔更好

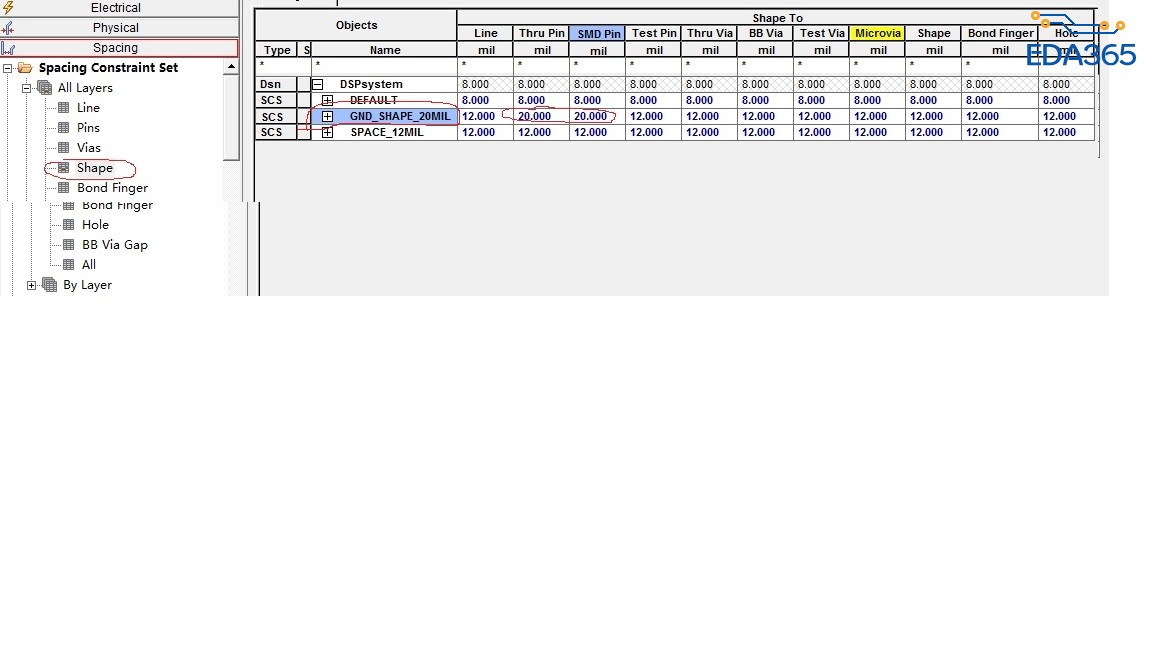

我已经解决了。在约束管理器spacing>shape新建约束项,shape to thru pin设置为20mil。然后在net中将把此约束赋值给gnd。

小编只是想避让电源插座那个pin呀,没说是整版呢!

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:PSM文件无法读取问题

下一篇:辅助边上加了光学定位点后板内还有必要再加吗?