- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3 T型地址线如何设置等长?

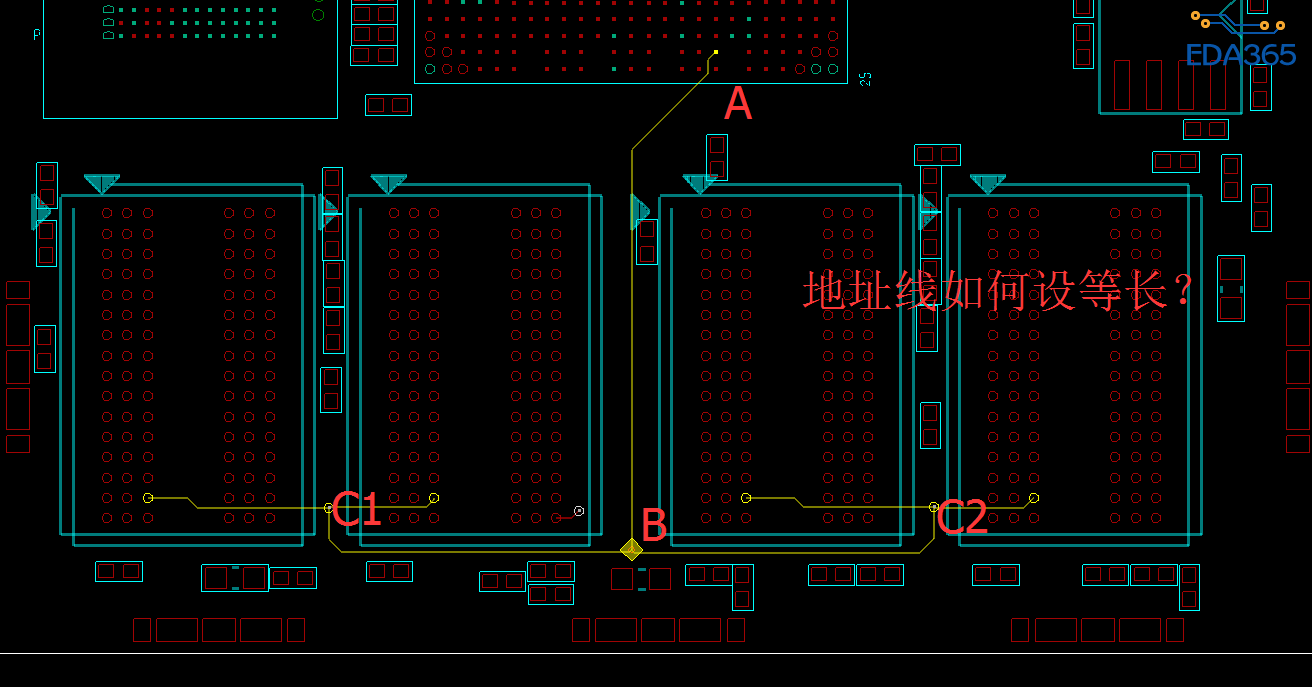

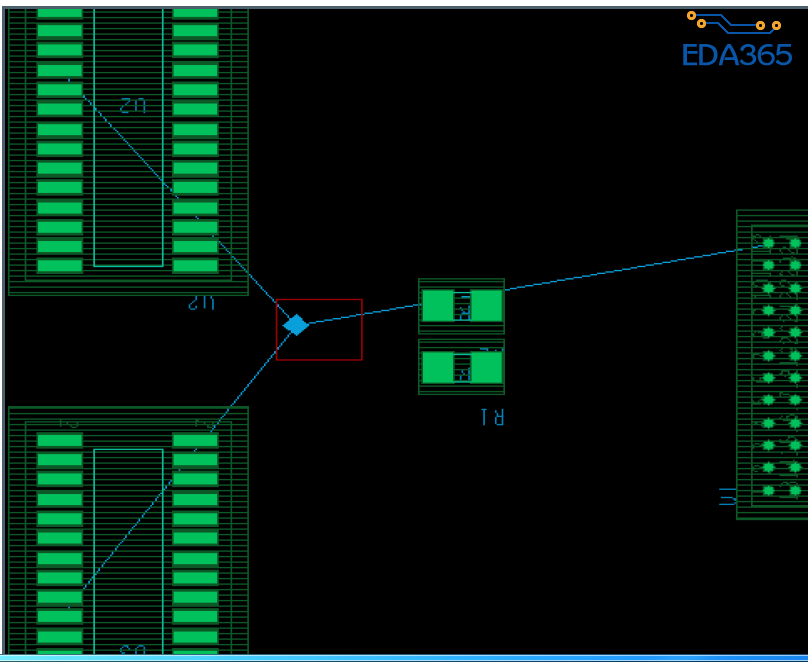

论坛找了很久就是没找到对的资料,如图4片DDR3 T型拓扑(走了一跟网络都在TOP层只作示范),数据线我知道怎么设置等长(D0-D7,DM,DQS0_DP/DN为一组,组内等长误差+-25mil)........。

但地址线怎么设置呢,加入了T点, 接下来如何分组等长? 所有A到B的线为一组等长,B到C1的线为一组等长,B到C2的线为一组再等长? 求耐心指教

大家快来啊

A-B等长,B-C1和C2一组等长

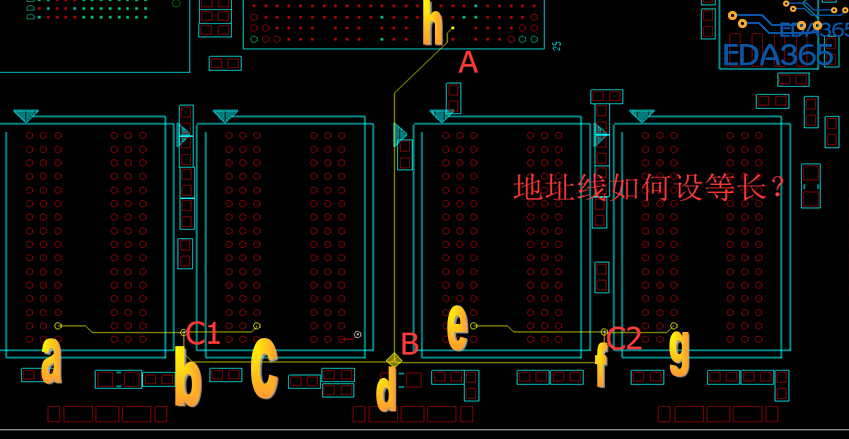

地址线A1-An:ab=cd=ef=fg所有地址线等长 bd=df所有地址线等长

hd所有地址线等长

大师的意思是说所以A-B段的所有地址线(A0 A1 A2 A3......A15....)做成一个MGOUP1等长;然后B-C1 的所有线跟B-C2的所有线一起构成一个MGOUP2等长。 对不? 另外我们做等长的最终目的是不是实现所有不同地址网络之间等长,然后我们就通过上面的分段来实现整条网络等长?

是这样的

1>hd所有地址线等长: 只设一个MGrp,创建pinpair 等长,这个比较好做。

2>bd=df所有地址线等长:一条网络就有2段这样的线,2对pinpair;25条地址网络,就有50对pinpair,这50对pinpair都做成一个MGrp吗?bd0,df0,bd1,df1,bd2,df2...........bdn,dfn这么多都做成一个MGrp?

3>ab=bc=ef=fg所有地址线等长: 一条网络就有4小段,4对pinpair;25条地址网络,就有100对pinpair,这100对pinpair都做成一个MGrp吗? (ab0,bc0,ef0,fg0,ab1,bc1,ef1,fg1.......abn,bcn,efn,fgn 这么多pinpair都做成一个MGrp?)

再求大师们的解答

hd所有地址线等长,一个MGrp,bd=df所有地址线等长,一个MGrp,这两条必须要做,ab=bc=ef=fg所有地址线等长,如果是正反两面各放两片的话,做起来也简单,经常也是会做的,四片放在同一面,不做也行,具体你可以看看你们CPU的官方layout guide,包括等长误差控制要以手册为准,国产CPU比较坑,建议比控制比手册严格些

嗯,非常感谢! 今天我就刨根问到底啊,还有问题如下:

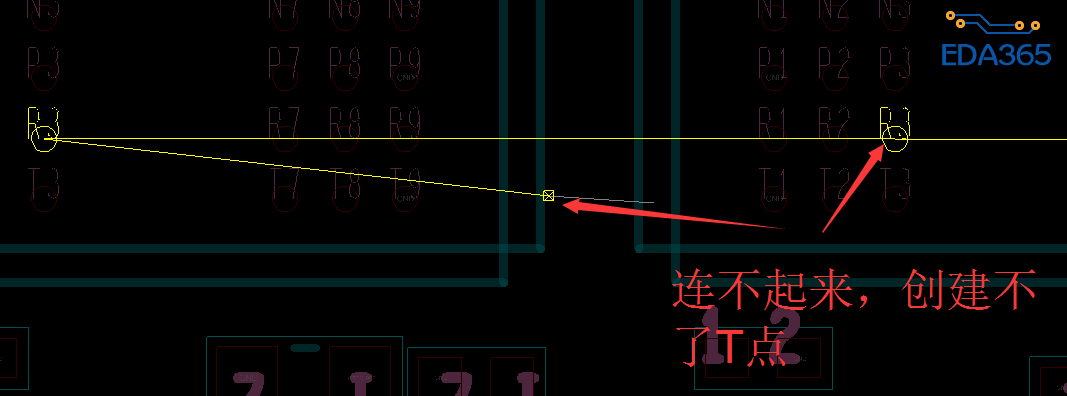

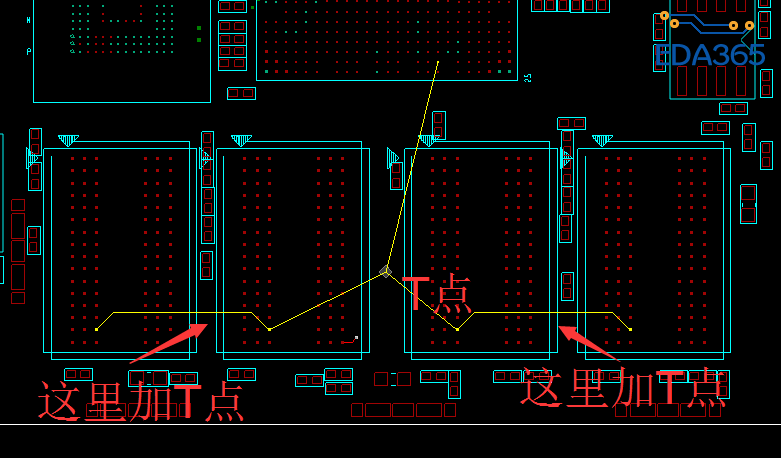

1> b点,f点貌似只能打过孔,加不进T点(d点能加入T点),难道要做一个封装?

2> 地址线网络间等长误差一般为多少?

3> 若地址线网络等长误差为+-50mil的话,那我这样分3类去等长,每一类等长误差不是要缩小为+-17mil(50/3) ? 这样总的等长误差才是+-50mil. (分两组hd,bd=df等长的话,每一组等长误差是不是为+-25mil?).

4> 上面讲的是通过一个T点分段来实现整条网络等长, 我看到有些方案没运用到T点,直接ha=hc所有地址线为一组等长,设置左边两边DDR3的等长就好了,右边不管直接copy 。这样是否可行?

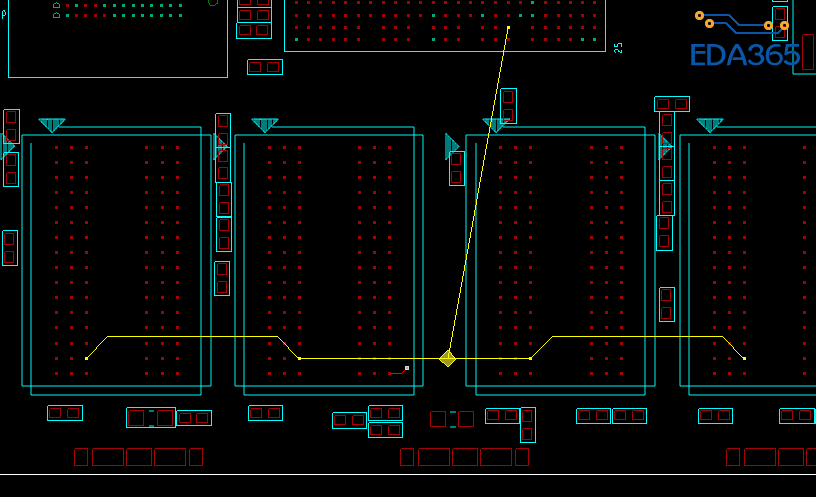

第一个问题,T点可以加的,你再试试,注意同一组线上的过孔数量必须一致,每个过孔都会带来很大的延迟,建议少打孔,包括数据线

第二、三两个问题,地址线间等长误差以手册为主,总误差要短,分配的话不是平均分配,bd=df这种要求要严格,尽量做到误差10以内,甚者是5mil

第四个问题,对称COPE是layout常用的方法,省事很多

我还是创建不了左边两片DDR的T点,我的方法是logic---net schedule 右键单击左边DDR3的一个PIN ,然后拉出来右键insert T, 然后再点第二个PIN就是连不上

方法如下:1、添加T 型连接点。点击Logic-Net Schedule,单击你要设置网络的一个pin。在中间右键Insert T,加入T型连接点,然后去点击第二个pin,再回到T 型连接点,然后去点击第三个pin,右键done即可。

知道这个方法,中间的大T点可以加,但就是两片DDR之间的小T加不了,如图所示位置添加不成功。

复杂了吧。还是用fly-by模式吧。

fly-by,不能随便用的,要看你芯片支不支持,不然肯定出问题了。

www.only-ways.com

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:package dimemsion

下一篇:allegro约束管理器中net group、match group、pin pairs、net class、class-class...