- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电感下面走高速差分线-这样可以吗?

录入:edatop.com 点击:

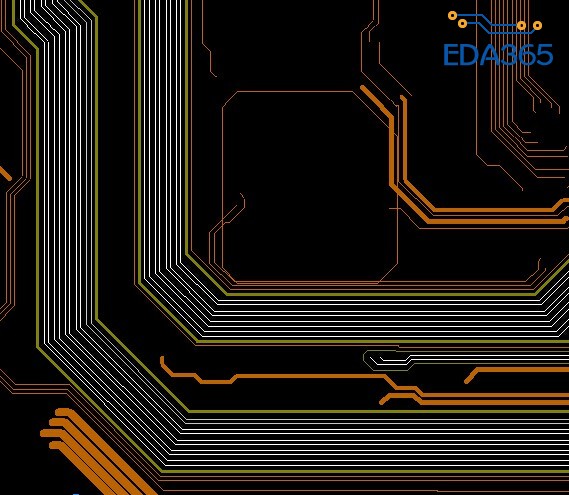

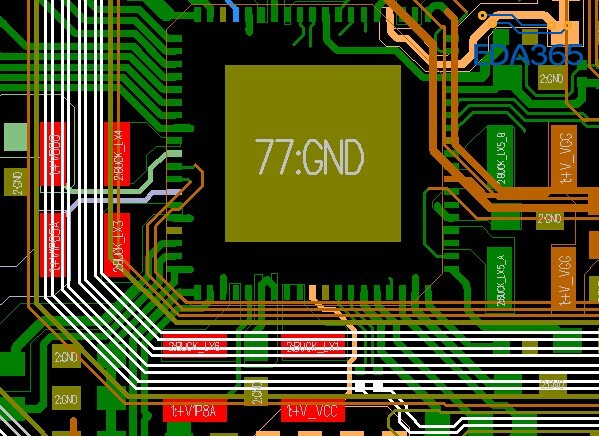

第一张图片是TOP ,2层是完整地,三层走单端线;第二张 4层走的高速差分线;但是大部分都有经过电感底下,

我认为这样是不行的,但是我的理论没法说服我们的layout工程师;现在求教各位大神

我认为这样是不行的,但是我的理论没法说服我们的layout工程师;现在求教各位大神

你自己意识问题,这样走线没有问题,你去说服layout只会让人家笑话你。理论上,哪怕只隔一层地,就不会干扰到。实际上就算临层干扰,问题也不会大。只是你们这些double e太苛刻罢了。

这样看比较清楚;

撑死算是不好,不至于到不行的程度.

差分本来抗干扰能力比较强,而且跟电感还隔了个地,如果特别不好调整,可以忍

最好当然是避免,不过这么走影响也不大

如果是高速切换DC-DC电感,能避开还是,避开吧,到时候调试有问题总要怀疑到这个上。

大电感大电流,电感下面不走线,不走线,不走线

确实是这样,但凡是板子没调试通,不管是软件还是硬件,第1个想到的就是检查layout

2个问题:1.确定这些都是电感而不是磁珠?2.层叠是top/G/S/S?

如果是隔了这么多层,是没有什么问题,放心吧,因为你毕竟是贴片的,如果是插件的就一定不行

个人觉得,只要领层不走线,就ok。但有空间调的画,我相信layout工程师会自己就调开的。

板子调不通的,都来检查layout.

为啥还要“睡服呢”?

直接动手就改了。本来做硬件就要避免各种不稳定的因素。

贴片中间隔了地层,问题不大

理论上不好,但是没空间怎么办呢。

看画的情况,估计你让他全部移开的可能性不大哦

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:想求PADS转ALLEGRO的方法

下一篇:怎么在all / layers 里建立BUS ,才能加入到rgn的rgn-classl里?