- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

8层板阻抗参考平面的疑问

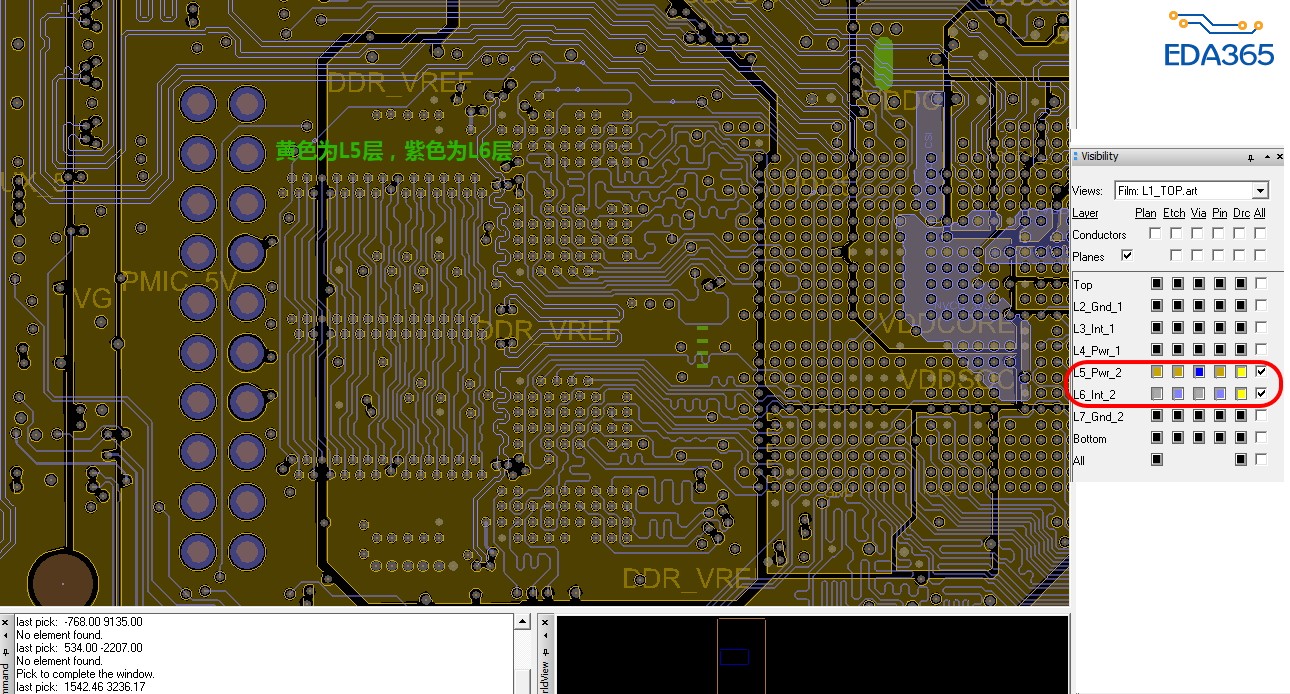

其中L2,L7都是完整的GND。L4、L5为电源(不完整)。上图中,紫色的为DDR数据线,在L6层,那么L7是完整的GND,可做其参考平面,上图可见,DDR数据线跨越了L5的电源层,这是否意味着,这个板子阻抗匹配时,L6的参考平面只有L7一层 ? (同理L3的阻抗参考平面只有L2一层?)

如果同一块板子,A,B 两部分走线线宽一样,都要求50欧姆阻抗匹配,A部分走线有2个完整的参考平面(GND和电源),B部分走线有1个完整的参考平面,如果保证B部分的50欧姆阻抗,那么A部分由于有两个参考平面,是不是就不为50欧姆阻抗了?这种情况如何处理呢?

不为50,但是A B两部分走线的阻抗误差不大,可以忽略不计。

不为50,但是A B两部分走线的阻抗误差不大,可以忽略不计。

要考虑叠层之间的间距

首先,你要明白参考平面的意义。在这里,L6-L7的距离比L5-L6的距离应该是大不少的,比如,4vs10mil。那么可以认为L6信号回流绝大部分在L7层,L5层可以忽略不计。信号 阻抗,你多算算就知道,4VS10的话,这个10就是变成20,阻抗也没多大变化的~~~

1、看你PCB的整体厚度。2 叠层的时候 2/3 是一个core 3/4中间为一个 PP 如:pp>>core 跨分割可忽略不计。

对于内层信号控制阻抗是要考虑到上下两个参考层的,而不是只参考一个,小编的这个层叠结构理论上应该是l2,l3是一个core,l4,l5是一个core,l6,l7是一个core,这样的话理论上l6与l7会很近,相对于l5层因为中间是pp所以就厚了很多,通过si9000计算会发现PP介质厚到一定程度后阻抗变化会很小。对于小编的设计个人感觉如果空间允许的话尽量把ddr

内层阻抗计算是由两个相邻的参考层共同决定的,而非只有一个参考层,只能说l5层因为中间是PP厚度会更厚,可能影响不会像l7层那么明显,而且看小编的设计有些ddr的走线出现的跨分割情况,阻抗可能会不连续,回流路径也可能有问题,个人感觉如果空间允许的情况下适当加大ddr-vref的铜皮,使ddr走线的投影区域是两个相对的完整参考平面。希望对您有帮助。

学习了

遇到的这种情况 基本都是会看厚度确认参考面

所有内层走线的阻抗都是参考两个平面来计算的,因为第五层铜箔不连续,所以有一小段的阻抗会失真而已

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:关于3W和3H原则

下一篇:关于PCB设计中的一些问题