- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

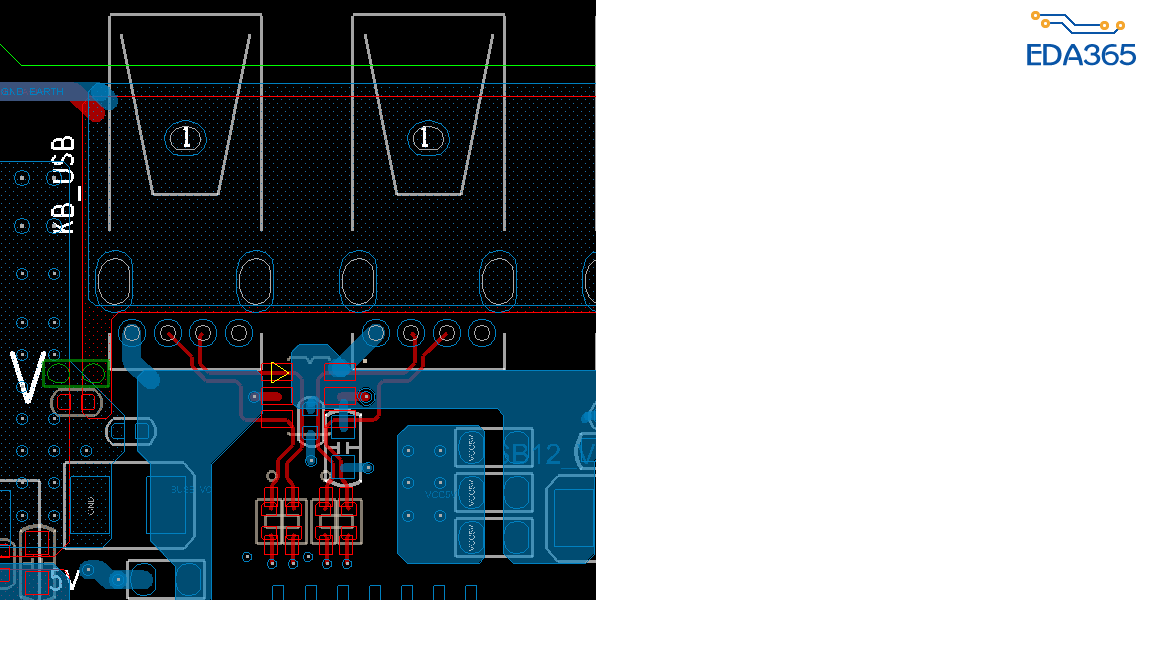

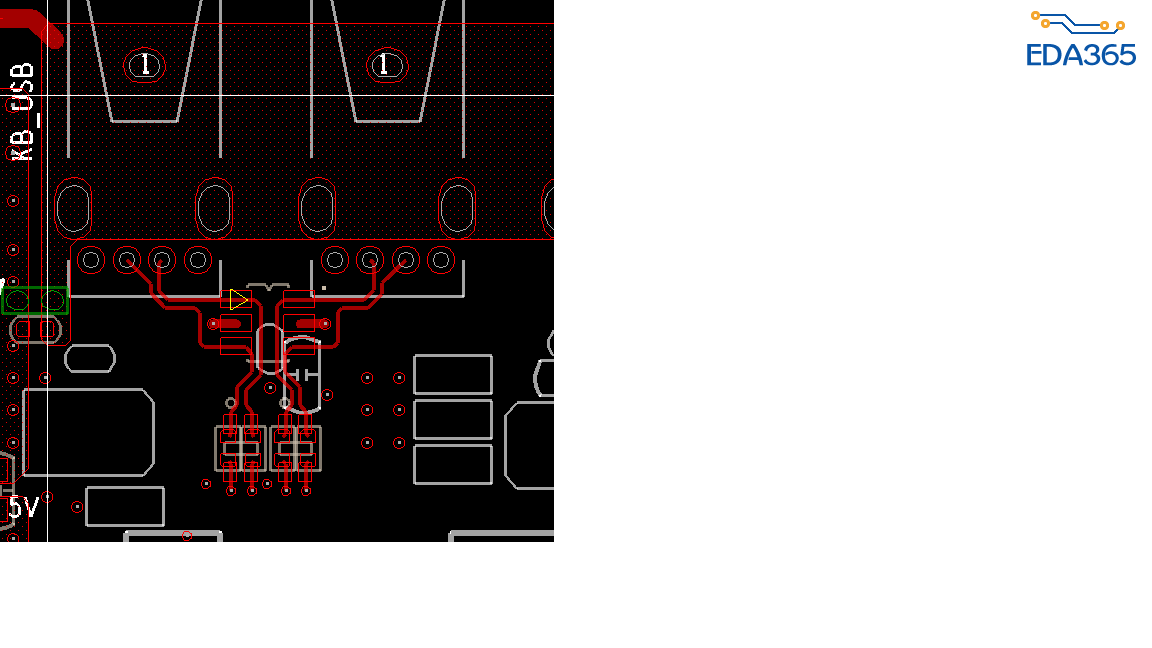

USB 抗干扰问题

4

看起来没啥问题。问一句, 你那个CMC还是什么,离USB接口那么近,能焊接上去么?焊接不上的话,对抗干扰还是有影响的

可以焊接上去在底层 USB 在表层

从usb接口到防护器件怎们没走差分呢?

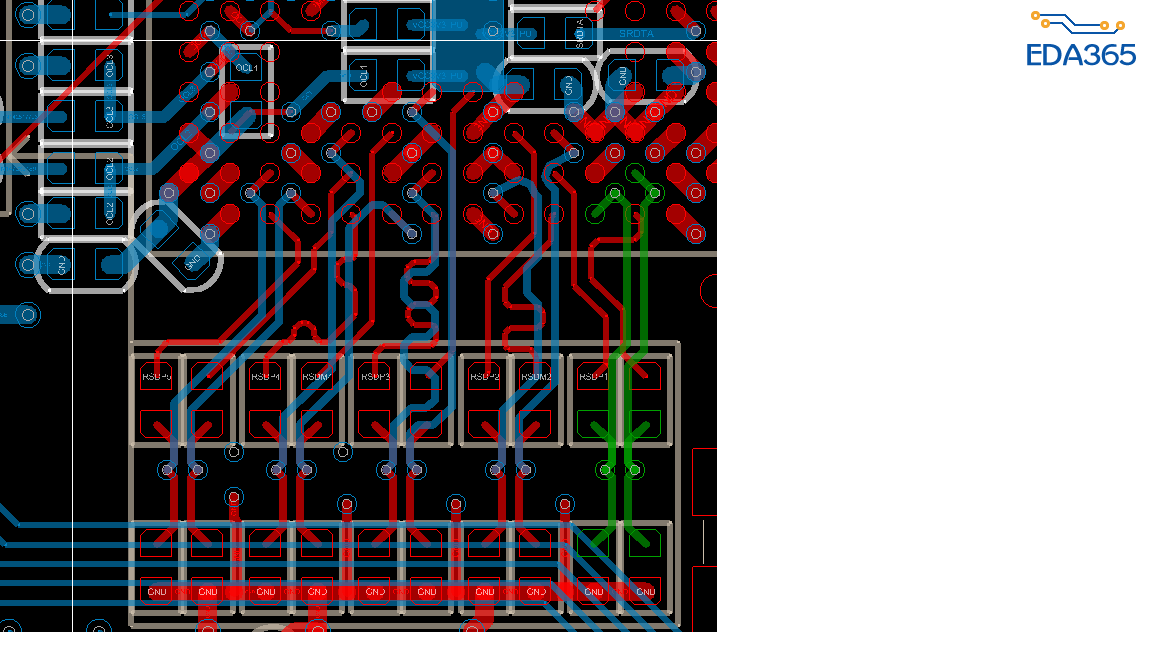

两个地之间的间距至少40mil,离得太近了EMC就过不了。USB内层走线跨分割严重吗?这里截图看不到。还有进来的那个芯片是防护芯片吗?感觉处理的不是很到位,走线。接到cpu处的那些匹配电阻,接地过孔太少了,那么多个共用3.4个过孔。

USB到 防护器件的线较短,就走了个类差分线,这样走下来正好等长要不也是得人工绕等长 从USB到下面的串接电阻 线长为437mil

两个gnd直接确实没有到 40mil 现在 目前的情况是 25mil 左右 但是隔离地到BUS的 gnd 引脚 较近 这个是 11mil 不知道这里 影响大不大

另外内层USB走线没有夸分割 USB 下面为整层的 gnd

最后的伴随gnd孔 我在多加几个

非常感谢

我感觉是不是我们公司测试的方法不对,他们拿了个打火机里面那个按下可以放电的东西,去打机壳。来模拟,USB受到的干扰。各位大神,你们的产品是怎么测试这方面的,求指导下

还可以这样啊?不是做SI吗?

个人愚见:

1、保护地和电源电的距离如6楼所说,加大;

2、USB的保护器件的接地问题,是否接保护地更为合适?

您好,关于第二条我想问下,如改为保护gnd 那usb 这个器件上面的gnd是不是也需要改为 保护地呢?

个人愚解 ,USB走线多粗?加粗到12MIL试试。另共模电感要用90欧的品牌货。

我是这么理解的,保护器件接到保护地,共模电路直接流向保护地,尽量使共模干扰不流经工作地。

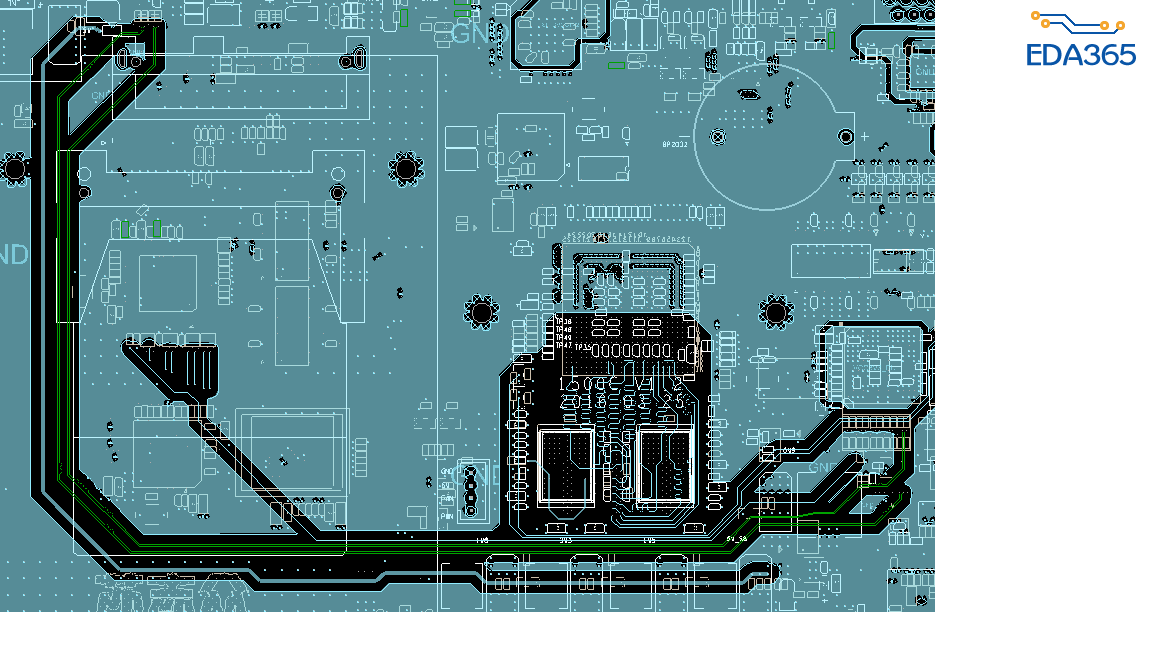

看看

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:选择多个shape中被层叠覆盖的那个shape

下一篇:17.2一直在打开升级网页