- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

插件pin内层不避让,求解

录入:edatop.com 点击:

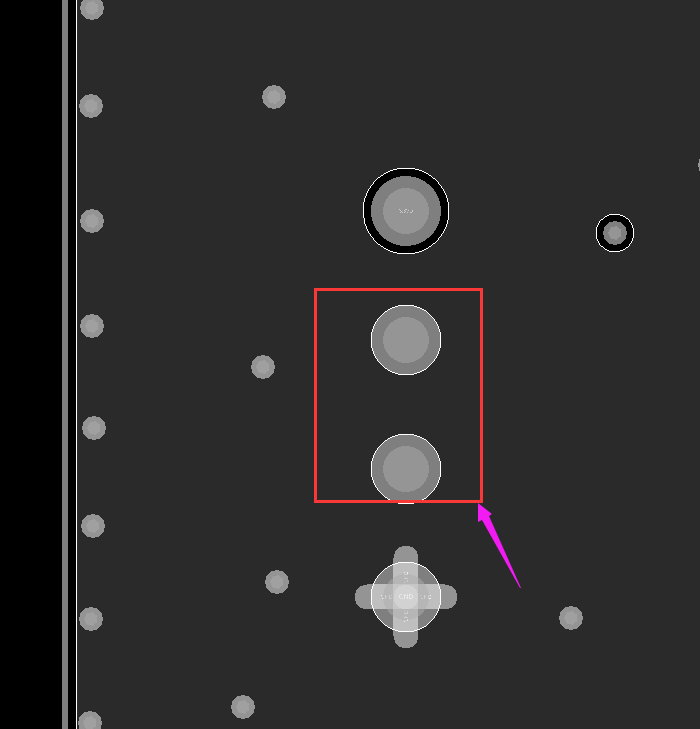

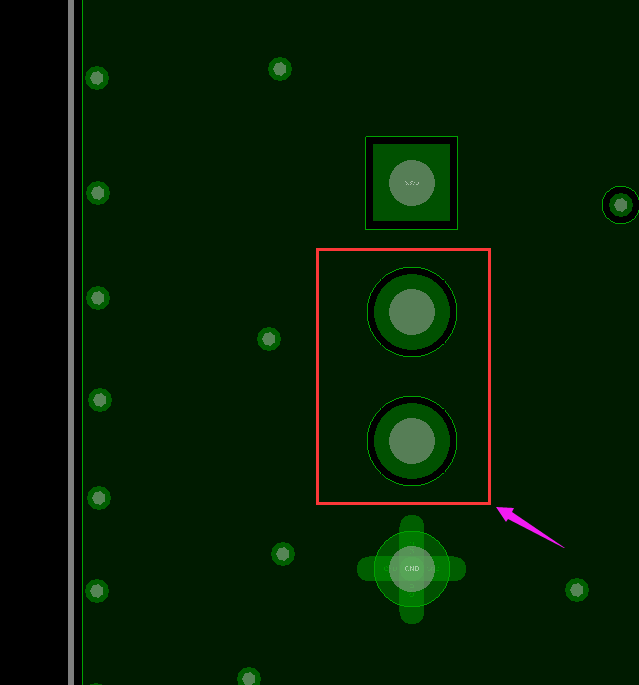

四层板,有一个插件的其中两个pin脚,TOP和BOT会和周边的GND网络避让,但是GND和VCC层不会避让,求大神指点是什么原因?

GND层

TOP层

求大神指点,感谢

看下规则设置是不是内层设的小啊

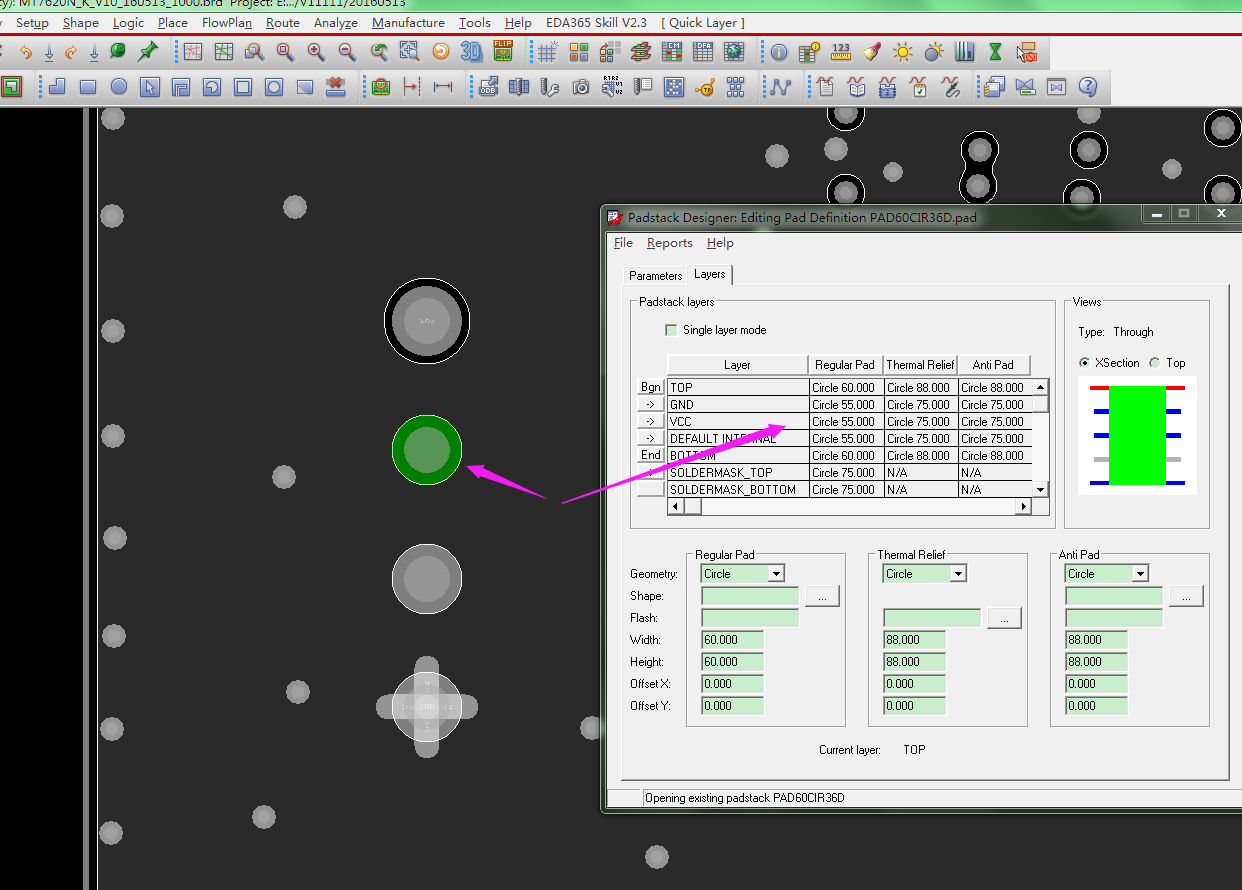

你看下这个盘是不是没设置ANTIPAD

内层的antipad有设吗

Antipad有设置,内层是正片,而且这两个pin脚也没有设置什么特殊的规则!

有设置,但是我内层都是正片,不是负片

内层没有设置小啊,你看我发的图,这个器件的另外一个pin都是有避让的,就这两个pin不避让,好奇怪

那看看是不是设置class to class或者针对net单独设置了...

在shape全局变量里面Clear里面的over size 改为0.0001就好了

学习了。

已解决,感谢各位热心帮助!

已解决,感谢各位热心帮助!

已解决,感谢各位热心帮助!

学习了

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:亲们 如何设置在allegro画板时,按左右剪头,一次只移动一个栅格距离?

下一篇:Allegro16.3铜皮出现异常,在线等帮助~~