- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请教高手,这几句英文啥意思,

录入:edatop.com 点击:

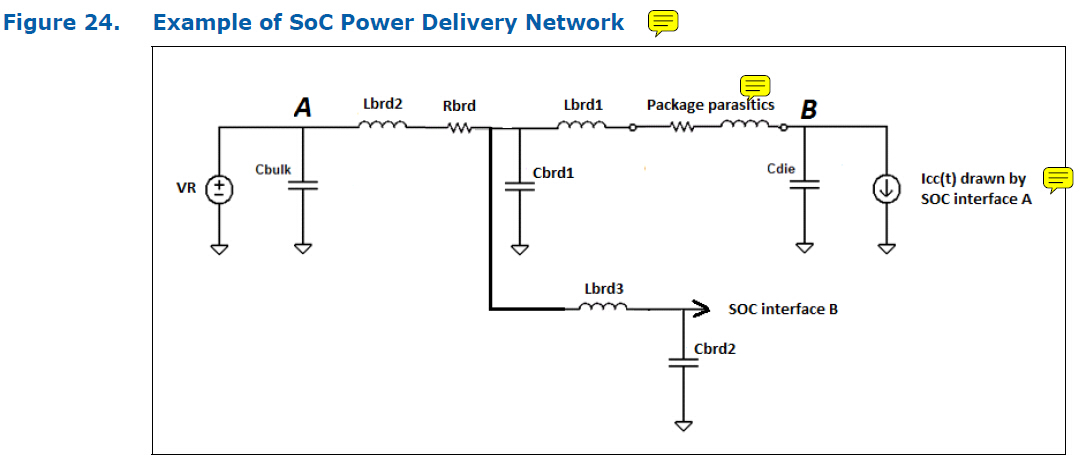

4.1.1.1 SOC Power Delivery Decoupling Requirement

The Decoupling Requirements table uses these specifications

•Nearest Board Capacitor(s): This is the type of cap to be populated near the SOC. All caps should be X5R material or better, and at least 4V rated. For “Interface A” in figure above, it’s Cbrd1. It can be in the form of:

•Max L from BGA Ball to Nearest BSC (nH): This is the maximum inductance from the listed ball to the nearest board cap on bottom side of the board. For the example above, it’s Lbrd1.

•Max L from BGA Ball to nearest ESC/MLCC (nH): This is the maximum inductance from the listed ball to the nearest board cap at top side:

—ESC: decoupling placed at edge side of package

—MLCC: lower frequency cap of 0603/0805 between BGA and VR

•Max L / R from Ball(s) to Bulk: This is the board routing requirement back to the VR bulk cap.

•Isolation Scheme: Board routing that requires isolation scheme to avoid noise coupling within the similar power supply.

主要是说SOC 电源的去耦要求:

最近点的板子电容:放在soc旁边的电容。 所有的电容温度特性要求至少X5R以上,额定电压至少4v.

上图中的A面,是Cbrd1,知道的是板子的电容值,可以如下组成:

从BGA到最近的背面电容的最大电感值,即Lbrd1。

从BGA到最近的ESC/MLCC的最大电感值

板子的走线到VR的大电容的最大阻值和容值

板子走线注意隔绝电源的噪声

实在看不明白。

这里的 BSC(指背面电容),ESC/MLCC(边侧电容/多层陶瓷电容)

其它英文就靠你们了。

隔绝 怎么可能。

百度翻译的,不要在意这些细节

非常感谢! 应该就是这个意思!

Isolation Scheme 隔离计划