- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3地址控制走线长度

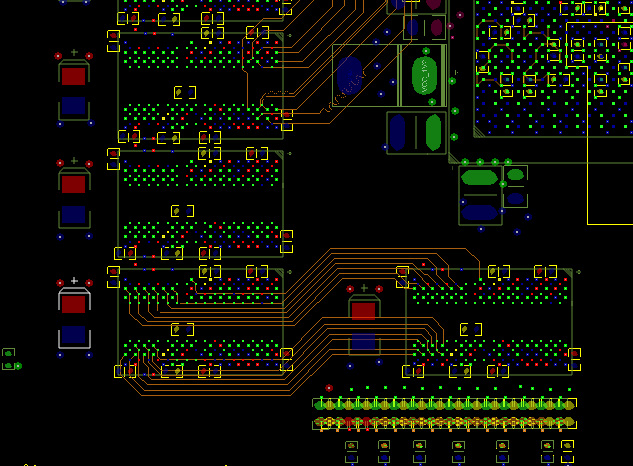

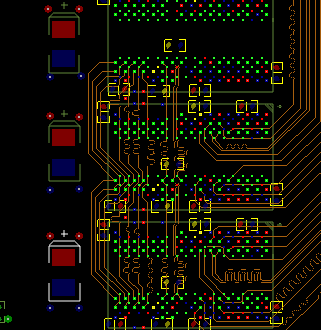

如图所示是4片DDR3,由于板子布局要求,最后一片只能放在其他片的右侧。图中的走线是两片DDR3互联的地址和控制线,由于布局只能这么走了。其他几片走线

如图所示是4片DDR3,由于板子布局要求,最后一片只能放在其他片的右侧。图中的走线是两片DDR3互联的地址和控制线,由于布局只能这么走了。其他几片走线 如上图所示。就这最后一片的走线突然变长了,会对整体有什么影响吗?这个长度现在差不多有1200mil,会不会太长了?

如上图所示。就这最后一片的走线突然变长了,会对整体有什么影响吗?这个长度现在差不多有1200mil,会不会太长了?单论等长1200mil是没问题,就是地址线的总长度你们有要求吗?或者看DATASHEET

地址线的要求是每片到BGA的距离相等 不是每片之间相等理论上是没问题的 只要组内等长就好

总长度倒是没有要求。个人感觉跑低速应该可以,但我需要跑到1300以上,不知道行不行

这样能跑高速吗?我需要跑到至少1300

主要是总长度是否有要求,你最好确认,因为他是的确有值的。等长每片之间要做等长。地址线最好做到10mil,数据做到5mil,你也可以做到更高的要求。如果特别重要,这么布局所有的只能为它让道啊。1300自我感觉时序控制的好,应该没问题。

学习,支持下

正反贴不好吗……

拉出去的好远……

1.CLK和地址线:(address/command/control midrange + 250) ±47 就是CLK要比地址控制命令的中间数值多250mil.CLK的等长正负47mil.

2.CLK到DQS长度:-879-10600

所以长度还是有要求的,不能比DQS多太多,也最好不要比DQS短。CLK最长多少还没看要要求,不清楚有没有

1.address/command/control:x1/x2/x3/x4/x5/x6/x7/x8/x9(includes package routing P0)

6.15/6.9/7.65/8.4/9.15/9.9/10.65/11.4/12.15 inches

2.Data Signals P0+L0+L1+L2:7.0 inches

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:旋转一个group有办法将选中的零件整个区域旋转90度吗

下一篇:有什么办法避免Dynamic shapes are out of date的警告从而顺利生成光绘文件