- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

差分线这样走OK吗?

录入:edatop.com 点击:

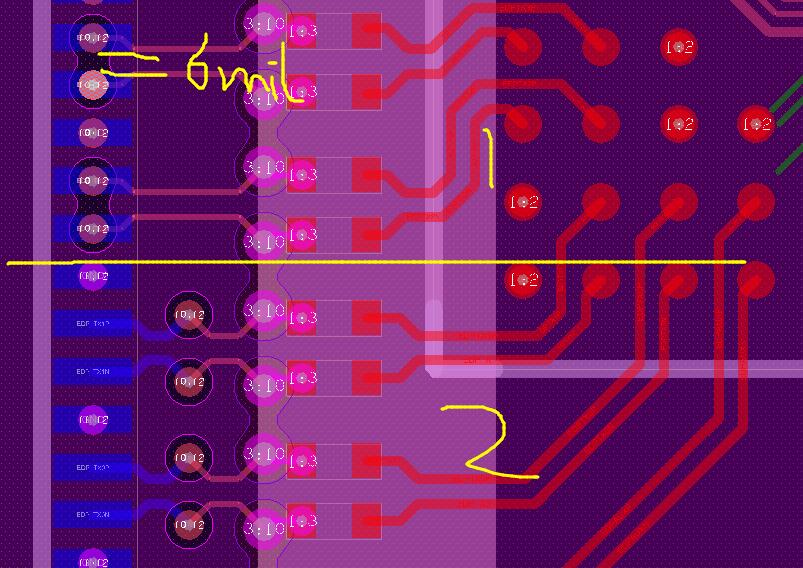

如图,哪种走法更好?

如图,哪种走法更好?差分线上的这对过孔要多近比较合适?我感觉后面的3:10孔间距太远了,我用的是系统默认的距离

谢谢大家

一般是与差分线的距离差不多,比如:差分线是:6MIL,那孔与孔也,6MIL.

谢谢

速率,仿真

一般过孔会选择35或者40mil的中心间距

这样的间距太大了点吧

一般intel平台 2.5G信号 差分对via中心间距25-50mil 差分对和差分对之间via中心间距>=50mil GND via<45mil以内

额外要求是:via尽量靠近连接器短线 差分对via尽量不要集中打 如果有空间

所以你上面的图 应该还可以优化

系统默认也是规则里面设置的default. 这个间距跟SI的要求有关。如果SI不关心,那么最小间距跟fab生产有关,也就是wall to wall的距离。最后,10~12这个孔距离跟3:10没有可比性,一个是微孔,一个是机械孔!

这样等长不好做,太短了

对内等长不好做,空间有点紧张

差异很小了已经 不需要在等长了 差异不到4ps

你怕有问题做个反焊盘拉高下阻抗就好了

,没问题

尽管不知道你差分线速率有多少,但是个人认为没必要去内层走那么一点。

没必要去内层走那么一点

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:我想任意设置格点值,请问快捷键语句该怎样写?求解,谢谢.

下一篇:在EDA学堂购买的课程可以反复看吗?会存在自己的账号下吗?