- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请教Allegro规则设置

录入:edatop.com 点击:

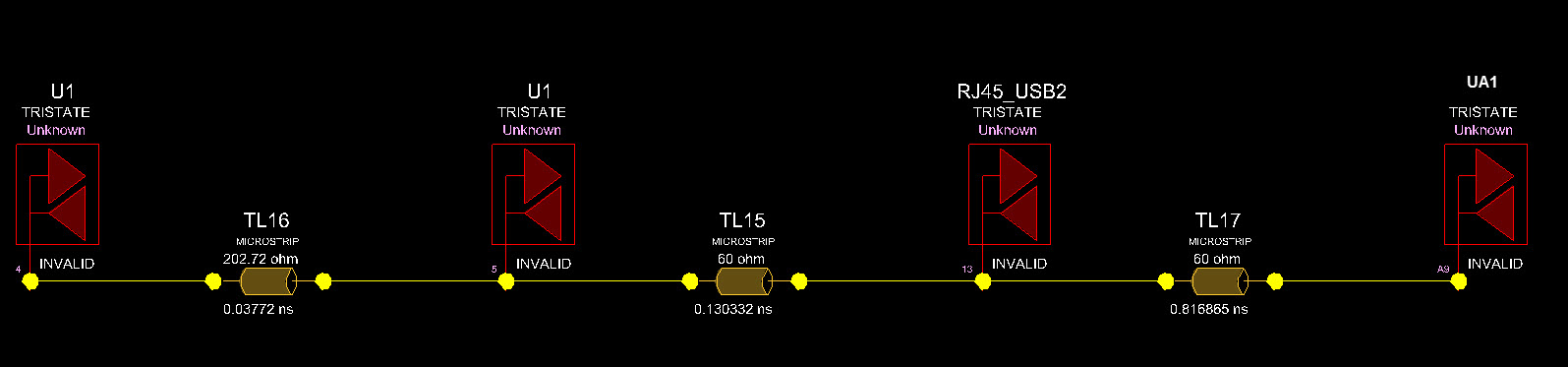

如下图一,差分信号从UA1发出,经过U1,到达RJ45_USB2连接器。U1的第4pin和第5pin是同一网络,第3pin和第6pin是同一网络,以此类推。

这种情况下,拓扑结构如图二所示,请问设置等长约束的时候,我怎么设置才能正确的得到UA1 -> U1 -> RJ45_USB2之间的走线长度?

多谢各位!

直接设置pinpair,UA1---RJ45_USB2,中间的可以忽略啊

修改拓扑成UA1 -> U1 -> RJ45_USB2

你好,怎么修改?给U1赋以什么样的器件模型?

这不是差分对走线么 还设置等长干嘛?

楼上在解

小编 正解!

单纯设rule的话不需要,把线断了,调一下这三个的位置,重连完事。然后再设constraint就可以了。否则会有ET DRC

支持pinpair UA1---RJ45_USB2

可以设X-NET

应该是条条大路通罗马,都可以的

如果不用做分段等长就直接设第一个点到最后一个点,如果需要做分段等长就需要设X NET。CM的设定一旦想通了其实很简单。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:请教:电容在板上的布局问题

下一篇:求助:16.6破解問題