- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

求助:16.6 void shape 功能

录入:edatop.com 点击:

平时在做封装时经常需要在 Etch层画shape 和line, 然后用line去分割shape为很多块。

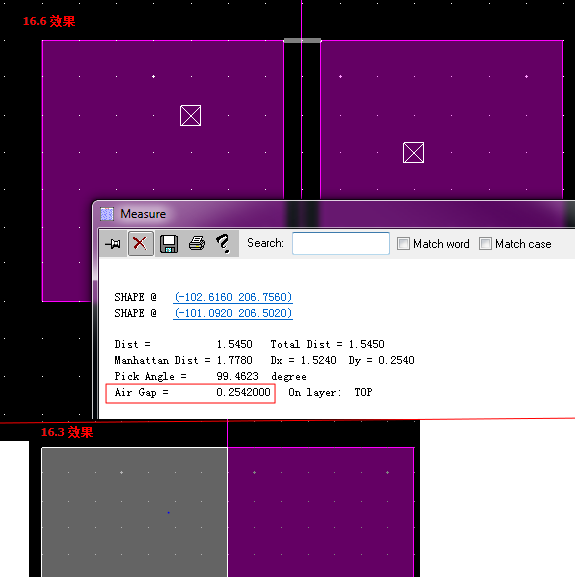

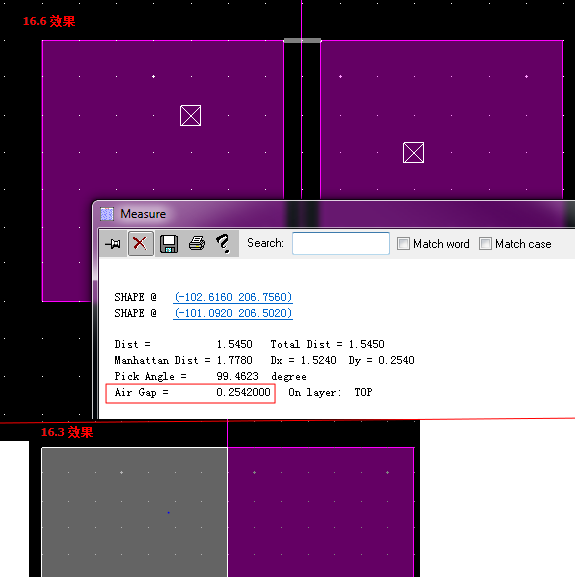

1. 之前用16.3的时候,当我用画好的line去void 整块shape之后, shape to shape 的airgap是0mil。

2. 现在转到16.6 发现void后 shape to shape 始终有10mil airgap。

求教, 如何消除这个10mil的airgap? P.S.本人已经试过将constraint manager 里面的shape to line、 shape to shape spacing 设置为0的方法, but failed。

1. 之前用16.3的时候,当我用画好的line去void 整块shape之后, shape to shape 的airgap是0mil。

2. 现在转到16.6 发现void后 shape to shape 始终有10mil airgap。

求教, 如何消除这个10mil的airgap? P.S.本人已经试过将constraint manager 里面的shape to line、 shape to shape spacing 设置为0的方法, but failed。

不行就手动拉过去。

恩, 目前我就这么干的。

只是有时候有圆弧状的line 去void会不太方便, 不知道大家还有没有别的方法。

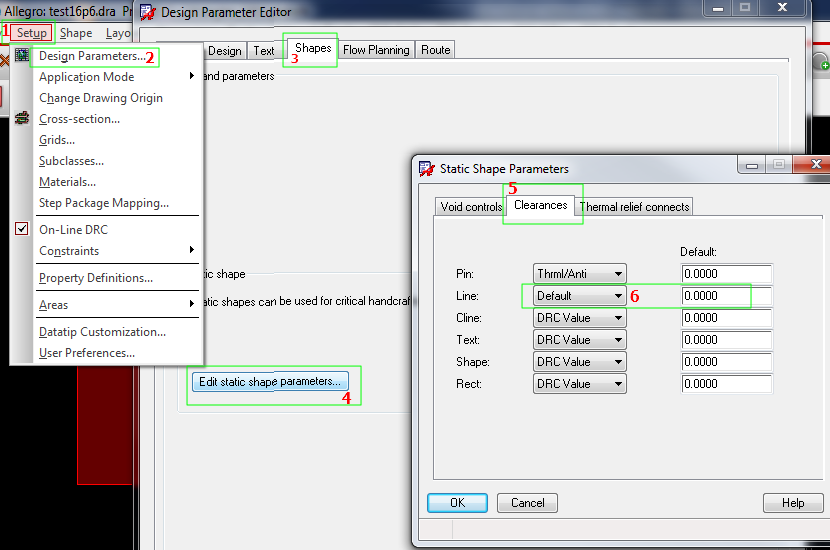

看看shape的global属性,里面估计设置了

选中shape,点击右键。有个shape的参数设置。有个clean shape 把line to shape DRC改为default。

多亏提醒, thankyou

good job, I show as below

做封装我怎么用不上这个功能?你做什么

一些相对复杂的器件的推荐footprint会给不同区域的元器件摆放设置不同的限高,我们会给placeboundtop分shape定义的。