- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR高频500M跑不起来,可以跑低频200M,pcb有问题?

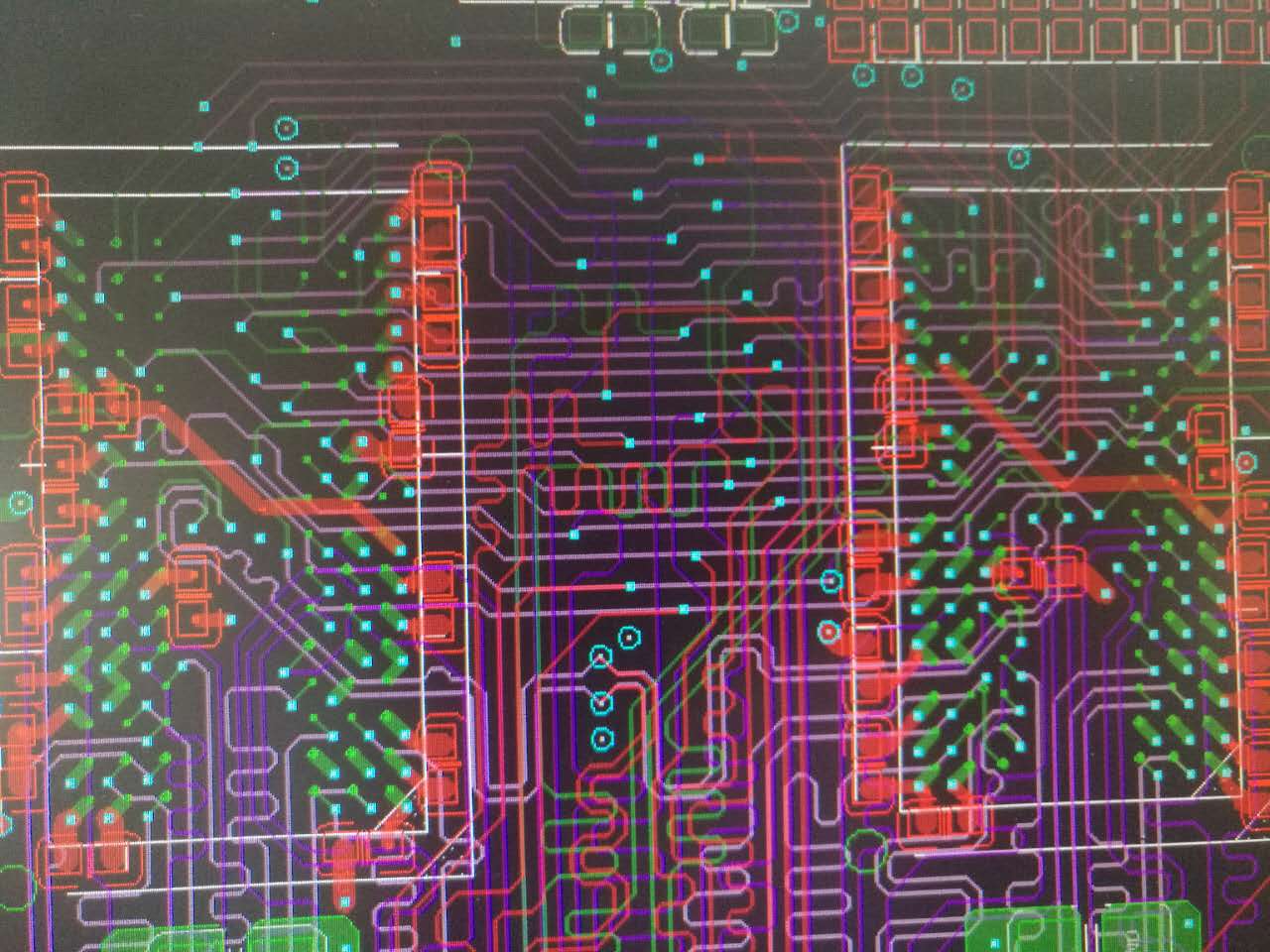

主芯片用的xilink:xc7z020-1CLG400C 位号U1

DDR :MT41J128M16HA-15E 2片 T型结构

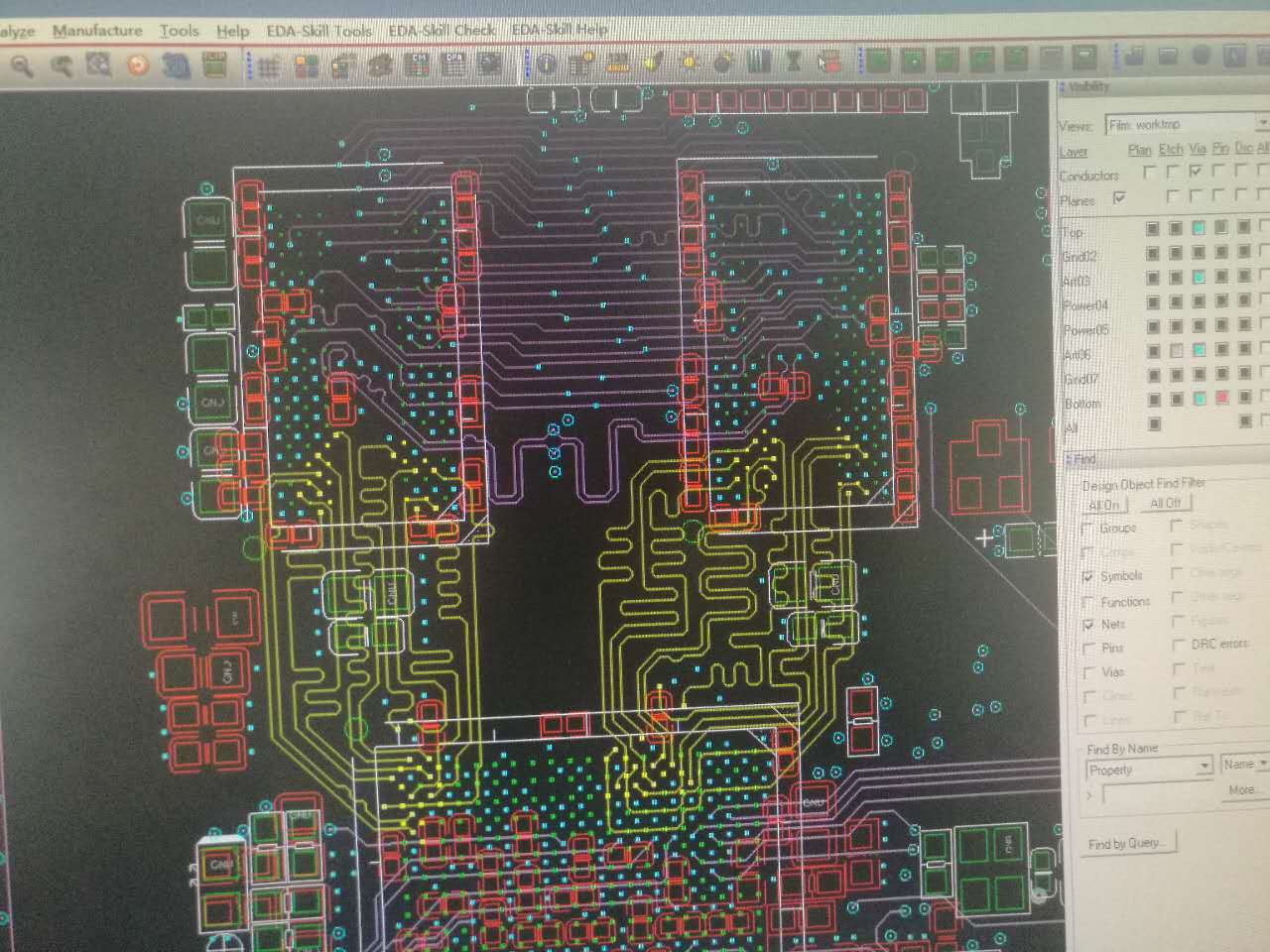

层叠:TOP01-GND02-SINGLE03-POWER04-POWER05-SIGNLE06-GND07-BOTTOM

数据地址线都是走5mil,间距10mil,50欧阻抗,差分对100欧

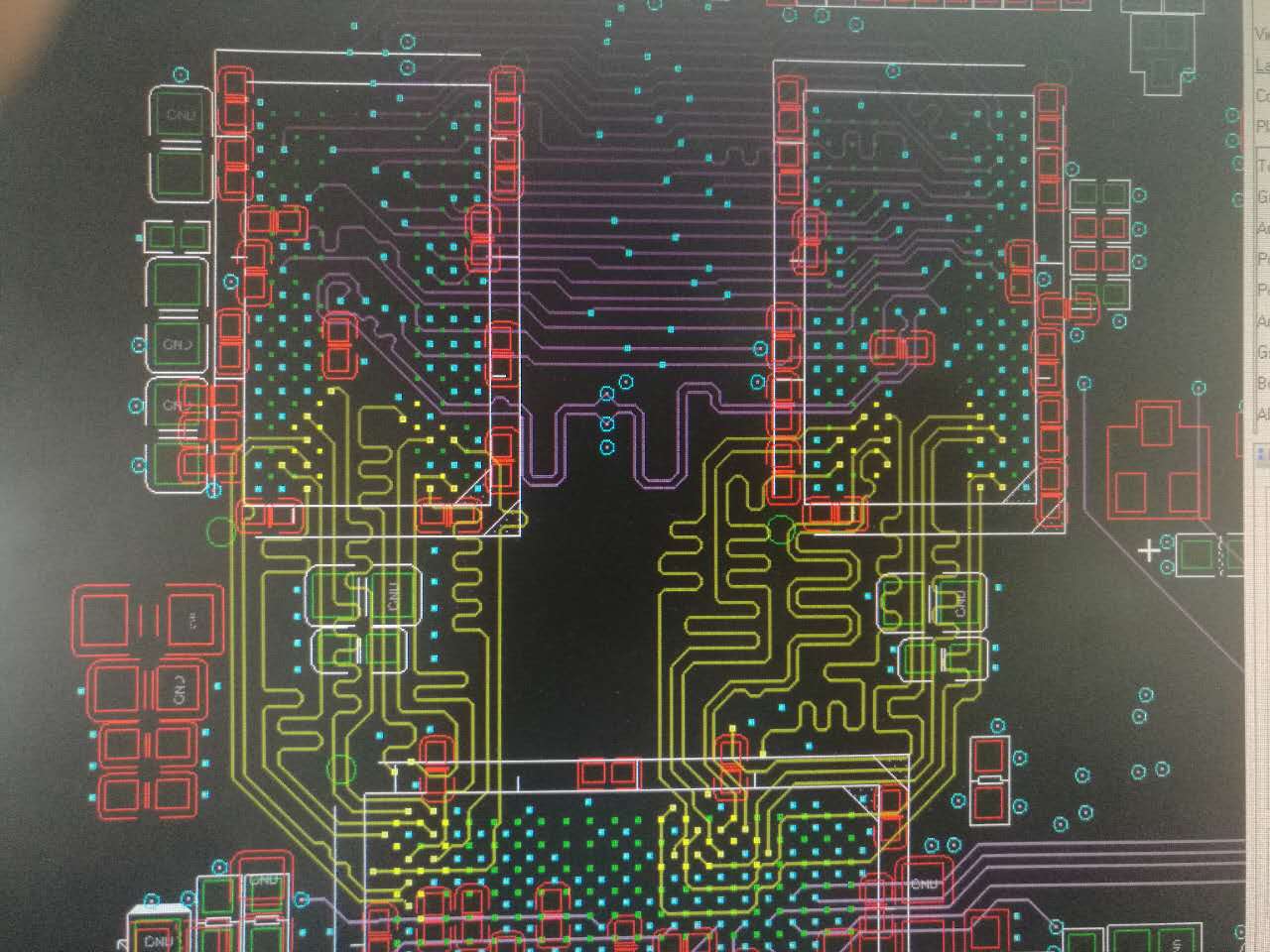

左边的是U3,右边是U2,U1在下

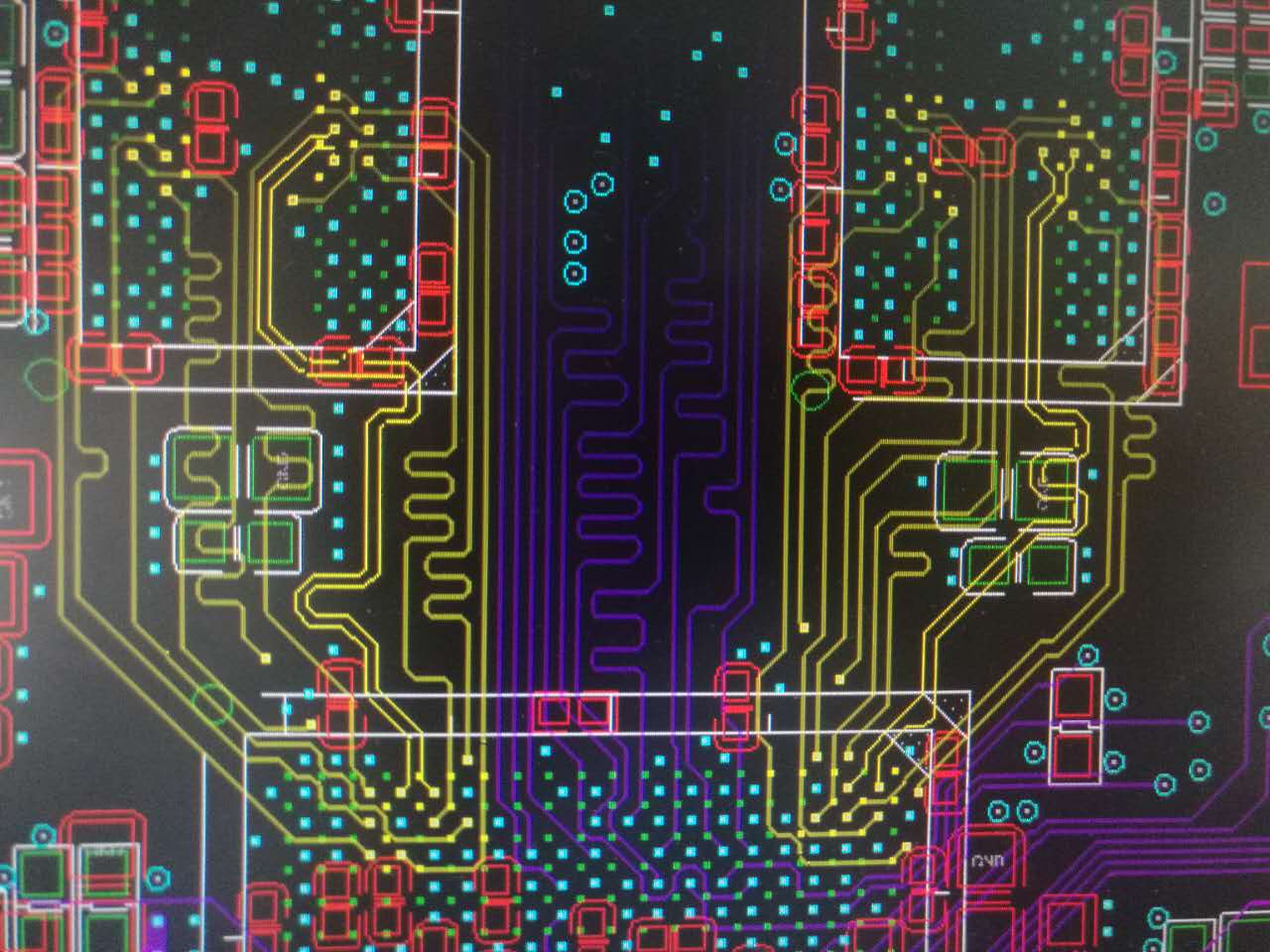

数据线:每11个为一组,U2上是D0-D15,D0-D7组走第三层,最长912mil,D8-D14组走第6层,最长1100mil;U3上是D16-D31,D16-D23组走第三层,最长1004mil,D24-D31组走第6层,最长889mil;同组同层;数据线内误差是25mil,差分对误差是5mi,以DQSP为等长目标对象,共32位数据线D0-D31。

地址线:做U1到U2 等长误差25mil,时钟线1780mil;做U1到U3 等长误差25mil,时钟线1768mil,都是已DDR时钟信号为等长目标对象。U2到U3互联是同层6层,CPU到T点不同层,

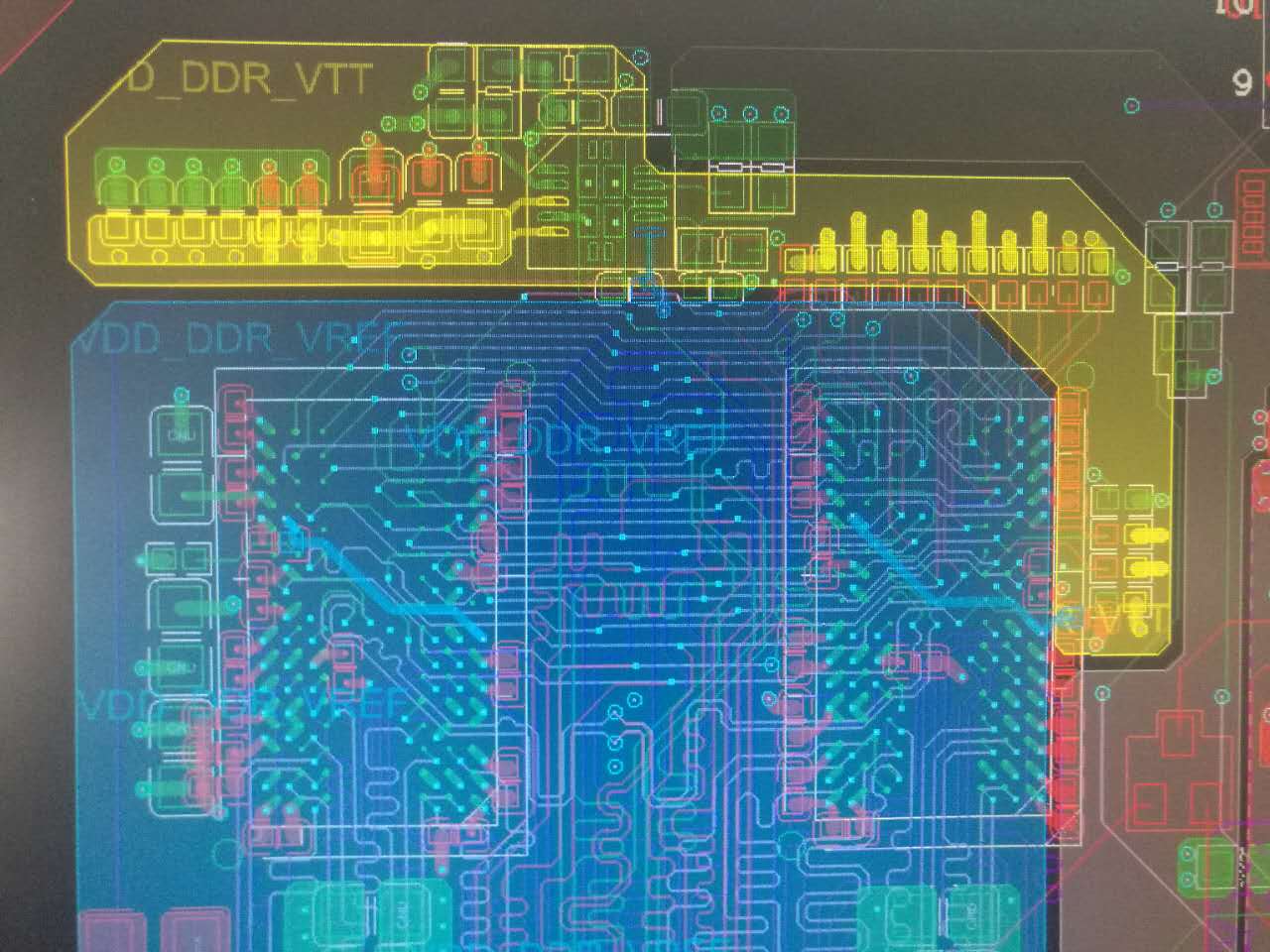

电源:上拉电阻在U2端,上拉电阻的电源芯片放在U2上方,VDD_DDR_VREF在第4层(由3v3转),VDD_DDR 在5层(由5V转)。DDR3信号没有跨越电源分割平面,共15位地址线A0-14。

反应现象:SDK里面跑过几次DDR TEST,没有报错,但是linux kernel启动的时候会报各种错误,然后僵死;在Vivado block design 里把DDR时钟从533Mhz降到200Mhz,linux可以正常启动。

问题1:只能跑低频,pcb有问题?

问题2:2片DDR组成的内存多大?

第6层:

5层全铺VDD_DDR电源,2、7层铺gnd。

第4层电源

第三层,左右为数据线

所有打开

截个图多好说明的,讲这么多,在说了你也没有提出实质性问题

把图发上来

板子画的有问题 没有满足规格

跑不起来是什么意思? 用xilinx DDR3 ip测试下 如果是读写偶尔有错误 的确是走线问题了 而且500M时钟 的确比较难做的 最近恰好在做这块 比较熟悉

还望赐教一下,那个地方出错了,感谢

SDK里面跑过几次DDR TEST,没有报错,但是linux kernel启动的时候会报各种错误,然后僵死;在Vivado block design 里把DDR时钟从533Mhz降到200Mhz,linux可以正常启动。

zynq7 应该也可以单独测试DDR3部分 意思就是 用纯逻辑设计读写不同频率试试 可以很清楚确定是否有问题 可以不要一来就跑cpu 你这样很难确定哪里出问题了

不知道你是做C开发的还是verilog的 让你们搞逻辑设计的人试试

我最近也发了贴,也是DDR的,我那个项目有8块单板,分两种功能,4块LVDS接口,4块RS422接口,最近逻辑在调试的时候发现有1块LVDS在800M的工作时钟下不能link,DQS找不到DQ,其余3块没问题,而RS422接口的单板有3块不能link,有1块可以正常工作,这个我就纳闷了,到底什么情况啊,求大神指导,谢谢!

小编,搞定了没,我也遇到类似的问题,一个多礼拜了,还没找到问题的解决办法。

不知道你这DDR绕线是不是按规格书上要求的去绕的,感觉你这个数据线每根都绕了,这样长度增加,不知是否超出了ddr的匹配长度

有没想过把地址线走在内层试试 感觉绕线也有问题 怎么组内每根都有绕线

数据线最远的在外面,所以一组内的其他的都绕了,数据线最远在内层,但是BGA是在最远处,这样他就最远了,所以一组内的其他的都绕了

地址线,ddr互联在内层,T点到cpu部分在内层,部分在顶层底层。因为CPU到t点同层走不出来,地址线在内层的话,横一个层,竖一个层。

你的是DDR几啊?看你布局VTT好像有问题哦?

建议DDR3一般走FLY-BY拓扑,你的VTT端接放最后,分支STUB尽量短,

你现在的T是芯片要求的吗?

另外建议你的VTT电容靠近端接电阻放点,现在全放右边的,走线还可以在紧缩一点,中间电源地PIN可以错开调一下留个通道出来

这个贴有些FANOUT可以参考一下

http://www.eda365.com/forum.php? ... amp;_dsign=14688e63

就叠层而言,建议中间可以不用两个电源层,4、5层可以把其中一个弄成地 , VTT和REF在走线层处理即可