- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请问这个是如何实现的,哪里可以设置,这样是否有风险

录入:edatop.com 点击:

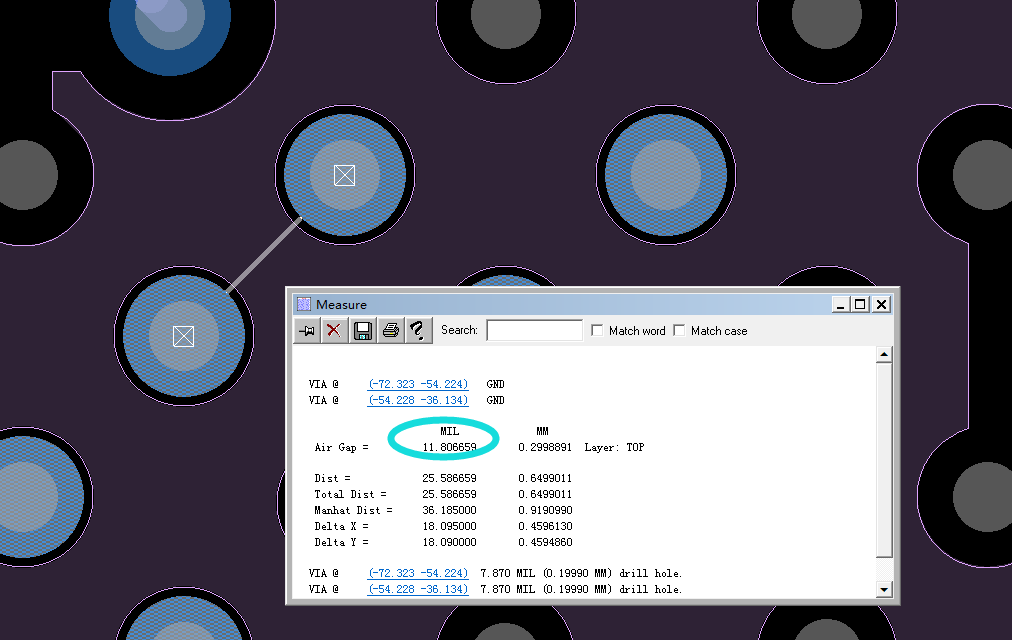

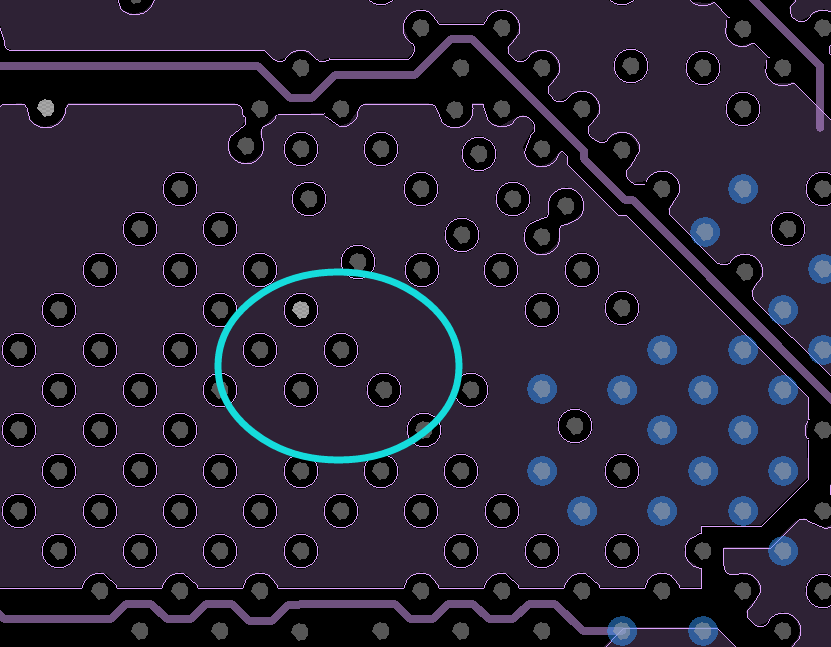

BGA中VIA TO VIA 间距小于12mil,铺铜时,铜皮不完整,DEMO板中是图2这样操作的,请问这个是如何实现的,哪里可以设置,这样是否有风险?

就是特殊区域的规则设施一下就好了,在规则里设置。只要满足板厂的加工能力就可以,风险比较小。

无盘设计,存在于平面层,使铜皮完整些,这样导致成型过孔不牢固吧!

fyi

也可以在输出光绘时,相应层勾选“Suppress unconnected pads”;不过不推荐间距这么近;

看来是我理解错了,大家都经验丰富啊!

内层在没有连接关系时去盘,只要保证和drill的间距就可以了,方法上面有了,很多产品都是这么做的,自然也是只要满足它的工艺要求,就没有什么风险。

学习

多谢

多谢,问过板厂了,能做到内层孔中心到线 四层0.15MM 六层0.18MM 八层0.22MM

隐藏内层孔环,保证孔与孔之间间距6mil以上就可以了~ 6mil的要是是厂家为了防止CAF风险

保证孔与孔之间间距5mil以上就可以了~

mark

学习了

RK方案的吧。这样做没问题。公司就是这样做的。4楼正解。不过建议是局部 区域,其他地方还是尽量不要这样做

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:可否分享下自己的快捷栏设置,就是ENV。

下一篇:元件封装高度设置