- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Cadence Allegro 如何避免过孔via 过于靠近焊盘 造成DFM问题

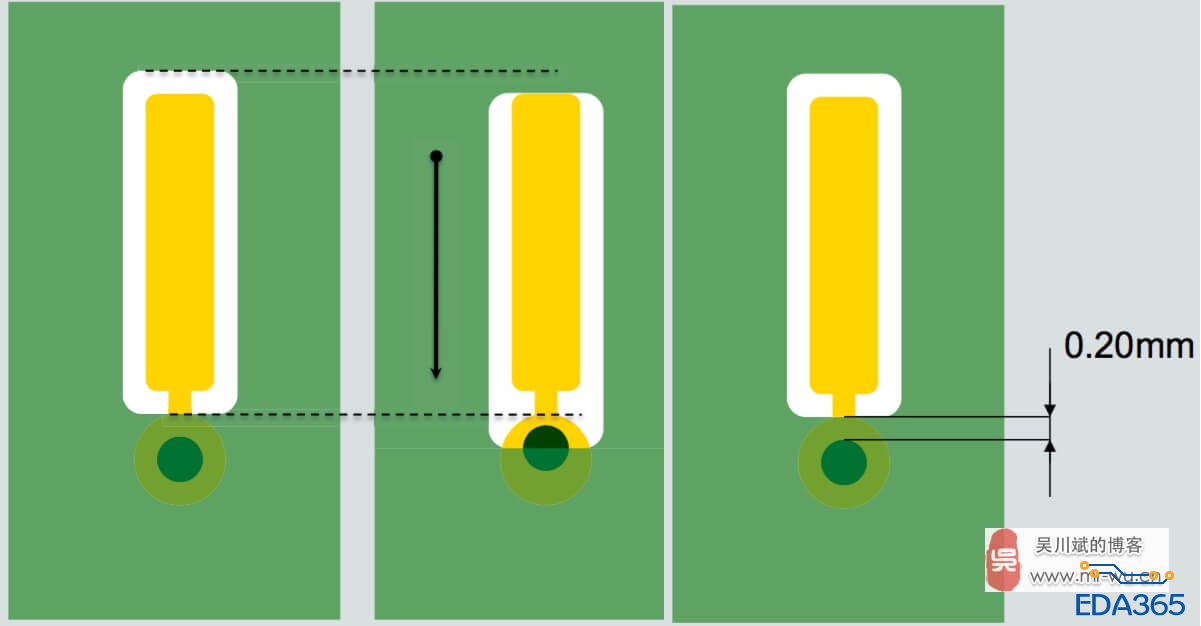

如果过孔via过于靠近焊盘,或者直接在焊盘上打过孔,在SMT时,就会漏锡造成器件引脚虚焊,而焊盘对面由于漏锡,会有短路的风险,除非你对过孔做「塞孔」工艺,但这样做会增加制板费用,如果不是空间受限的HDI板子,是建议大家别打盘中孔的,过孔孔环边离焊盘要拉开一定距离(0.2mm 8mil)。通常,我们做板时会要求板厂过孔盖油,但过孔过于靠近焊盘之后,会造成过孔部分开窗,焊盘上的焊锡便会流到过孔上。

那如何利用强大的 Cadence Allegro 规则引擎来避免我们在layout过程中无意的将过孔打得过于靠近焊盘,造成DFM违规风险呢?

Cadence Allegro 强大的 Constraint Manager 可以很方便的设定via与pad的间距以及是否允许在焊盘上打孔。

通过Allegro的菜单栏“Setup-> Constraints-> Constraint Manager…”打开「Allegro Constraint Manager」约束规则管理器。

在左侧的Spacing及Same Net Spacing设置不同网络及相关网络的间距规则约束。

在右侧的设置编辑界面中,可以双击「Thre Via To >>」展开via间距参数的设置,其中的All即使所有的间距统一进行设置,Line的值即是Via对line的最小间距要求,SMD pin则是Via与SMD pin的最小间距要求,以此类推。

对于禁止或者允许在焊盘上打孔,可以通过Physical这项规则约束设置实现,在Allow这一栏通过下拉菜单可以选择对应的规则, 如“NOT_ALLOWED”则是禁止在焊盘上打孔。

当然,对于允许在焊盘上打孔的器件,如BGA焊盘或者需要打开散热的焊盘,我们可以设置区域规则,针对BGA区域允许过孔打在焊盘上。

要想DRC显示基于过孔间距启用约束,还需要对Analysis Modes进行设置,在Constraint Manager界面中,点击菜单”Analyze->Analysis Modes”, 在弹出的Analysis Modes对话框中,勾选Spacing及Same Net Spacing 的 Hole To 为 On 状态。

:lol:lol

用绿油塞孔的成本和不塞孔会差很多么?

原文在这里:

http://www.mr-wu.cn/cadence-alle ... o-cheng-dfm-wen-ti/

我直接贴链接怎么提示非法呢?

将同名过孔的间距设大一点就行了

这个没事吧,不要打在焊盘上就行了,打的近点应该没事吧 ,不知道别人是怎样做的,这个距离我都没控制。