- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请教设置等长规则的问题

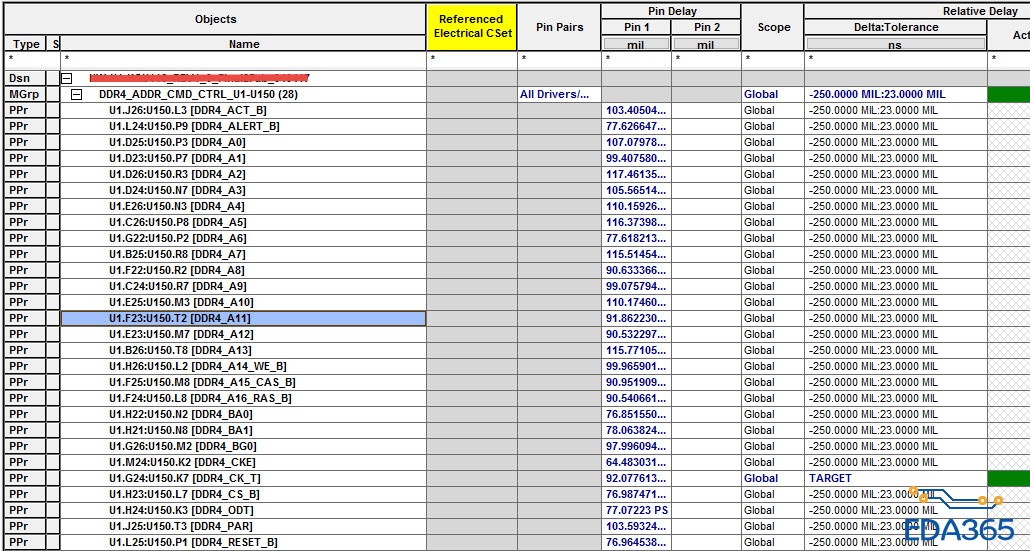

如下图所示,下图是某公版的设计,DDR4的控制/地址信号从主控芯片U1连到内存颗粒U150和U153,fly-by的拓扑(信号先连到U150再连到U153)。

在Constraint Manager的Relative Propagation Delay里需要设置所有控制/地址信号分别到U150和U153时等长,怎样才能像下图那样把所有U1到U150的长度挑出来,然后U1到U153的长度挑出来?

pinpair设规则的时候就设好

先设置PIN pair

谢谢你的回答! 是挨个网络设置pin pair,然后再把到相同芯片的pin pair归到同一个Match Group吗?

网络数量比较多,有没有批量设置pin pair的办法?我没找到批量设置的办法

谢谢你的回答! 是挨个网络设置pin pair,然后再把到相同芯片的pin pair归到同一个Match Group吗?

网络数量比较多,有没有批量设置pin pair的办法?我没找到批量设置的办法

在没有skill可用的时候,只能手动一个个设置了

好吧,谢谢你!

在Electrical约束里找一个你要设pinpar的net然后右键最下面有个SigXplorer,点击进去,然后set 里有个Constraint点下进去,然后再点Rel Prop Delay,在这里你可以设置多个pin-pin的等长拓扑,设置好之后保存更新到约束里,然后再到约束里找到和这个net拓扑相同的其它所有net,比如说所有的DDR data,然后加入到你刚才创建的那个拓扑就可以批量设置pin-pair的等长了data和地址因为拓扑不一样,要各找一个net建拓扑约束,不知道你能否看明白哦,可以网上找找教程

类似这个样子,这个是地址线的

看来学习的还很多

能看明白,谢谢你!

如下图,由于U1->U8->U9之后还有一个端接电阻,有些net会出错,把到电阻的pin pair分到MGrp里,还删不掉,有什么好办法吗?

出错的在到SigXplorer里重新建一个ecset,mg设置同一个名字就好,地址线拓扑不一样经常有这个问题。

sig不方便其实,乱匹配,比如你想所有的一组,它偏分四组,T点是这样的,烦

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:求教:allegro 16.6 大十字光标在画线,移动元件,量距离的时候就消失了

下一篇:allegro如何删除自定义的快捷键呢?