- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请大家帮忙,谢谢!

录入:edatop.com 点击:

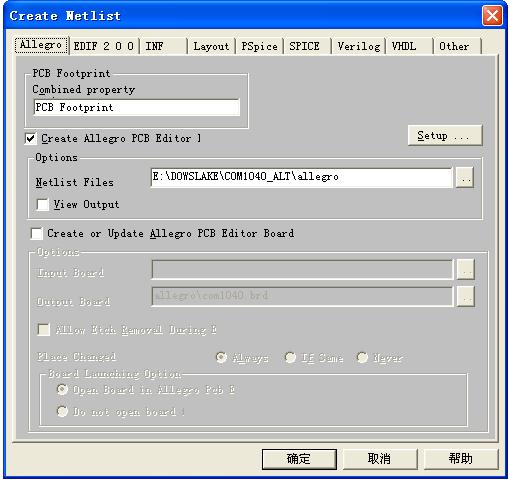

我在capture 的原理图中只画了一个元件,但在创建网表时在 create netlist中的 allegro

选项的input board一栏为空白,是啥原因?在pcb中打开output board 文件,pcb图中一个元件也

没有,是啥原因?

这样导入网表的

导出网表

用的是15.2

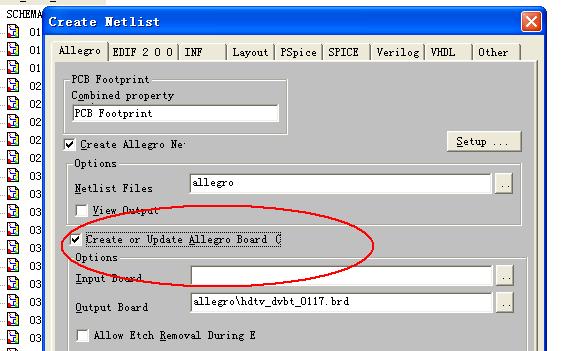

你二楼的图片是通过Capture导出网表,然后在Allegro中导入,没有问题,Allegro导入板子以后是不把元器件直接放在板子上的,确定你的setup--user preferences editor--design path--pad path/psm path都设置正确,在你的place--manually中应该就可以看到元器件。

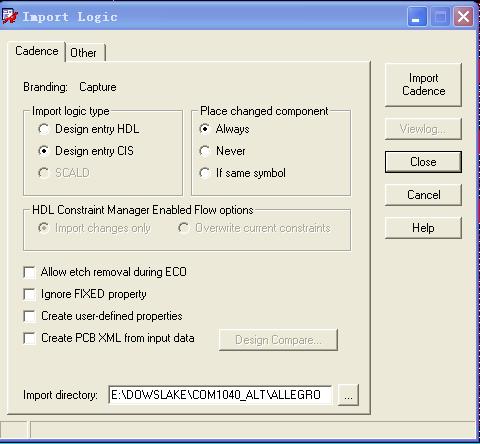

三楼的图片是Cadence提供的Capture直接导入Allegro的工具,需要选中红圈中选项,input board可以是新建的板子,导入成功后,系统会自动打开导入了网表的Allegro文件,既把二楼的两步合并。另外Input board也可以是已经设计过的文件,如果中间修改原理图而不想改变目前的设计,选择已有的input brd转到新的output brd即可。

路过

OK DING

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:紧急求助!请教SQ仿真问题!

下一篇:生成光绘文件