- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

该DRC错误,如何解决?

铺铜结束以后,出现很多DRC错误。都是Line to Shape Spacing问题,但感觉好像没有什么地方设置有问题。请各位大虾指点一下:

图中Shape为GND网络,动态填充。DRC错误处为一个直插元件pin。

LISTING: 1 element(s)

< DRC ERROR >

Class: DRC ERROR CLASS

Subclass: BOTTOM

Origin xy: (-22.07 3477.93)

CONSTRAINT: Line to Shape Spacing

CONSTRAINT SET: DEFAULT

CONSTRAINT TYPE: NET SPACING CONSTRAINTS

Constraint value: 5 MIL

Actual value: 0 MIL

- - - - - - - - - - - - - - - - - - - -

Element type: ODD-ANGLE LINE SEGMENT

Class: ETCH

Subclass: BOTTOM

segment:xy (162.63 3302.19) xy (-42.68 3507.50) width (5.00)

- - - - - - - - - - - - - - - - - - - -

Element type: ODD-ANGLE LINE SEGMENT

Class: ETCH

Subclass: BOTTOM

part of a connect line

Not on a Net

segment:xy (-22.07 3477.93) xy (-28.79 3471.21) width (15.00)

- - - - - - - - - - - - - - - - - - - -

[求助]该DRC错误,如何解决?

线和铜皮连的太少了就会报这个错误,可以把线往铜皮上再多连一些,或者你生成光绘看一下,要是光绘没问题你可以不用理会这个错误。

Allegro的网格铜箔不是很好,尤其又使用花焊盘更加不尽人意.

多谢二位的发言.

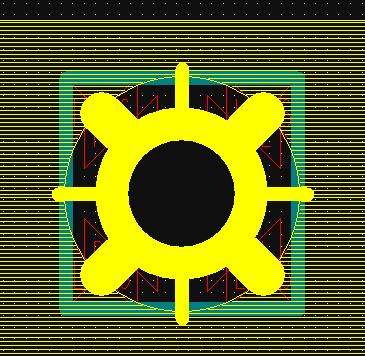

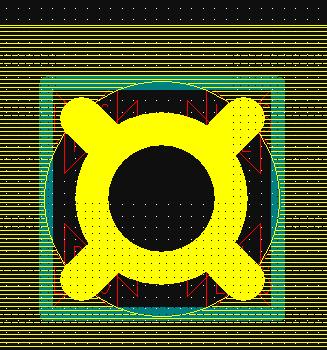

为了增加pin和铜皮的连接,将shape属性改为Thrugh Pin: 8 way connect,但还是一样,DRC依旧出现(只有solid连接时,才ok)。难道要手工连接pin到gnd网络?那样岂不是很愚蠢?

下面三个分别是用orthogonal connect, diag connenct, full connect的图片,是不是元件的这个 pin有问题?

Constraint value: 5 MIL

Actual value: 0 MIL

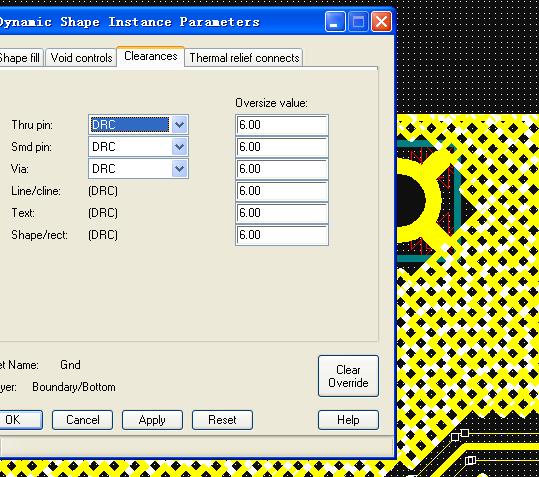

把use thermal oversize of 改为5个mil试试一下吧,

不知道行不行,dynamic shape instance parameters 这个窗口在哪呢?

我说的多连一点是指把线走的长一点,或者用DBDOCTOR检查一下一般错误就没了

我也碰到这种问题是:

第一次铺过铜又删掉(但没把花孔的SPOKE删除),重新铺铜造成的DRC.

要先把花孔的SPOKE删除,再重新铺铜。

hehe

应该没有大问题的,

可以当作没看见

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:请教个通过BRD文件导出封装的问题

下一篇:请问如果我要用新的过也要自己做才行吗