- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PowerPCB转Allegro碰到的问题?

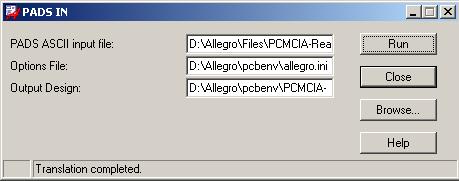

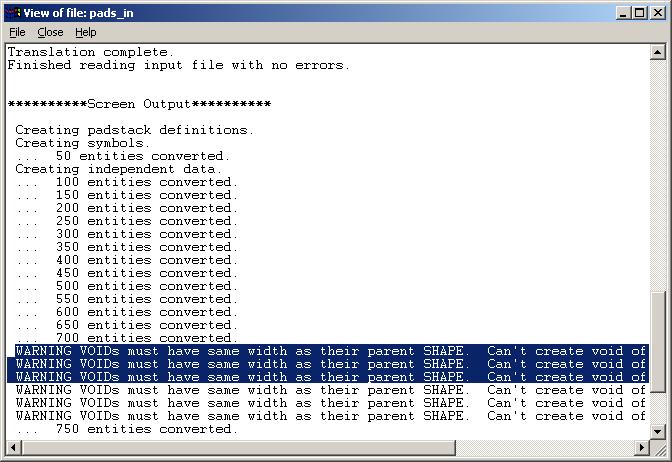

文件导入没问题,但就是看不到东西,板子里面什么也没有,用Viewlog查看一下,发现有如下同类问题:

D:\Allegro\Files\PCMCIA-ReaderV3.asc.

Reading PADS ASCII file header.

Version = PowerPCB3.5

Route Layers = 2

Units = METRIC

Hatch mode = Vertical / Horizontal

Hatch grid = 7.870079, angle = 0.000000, anti-pad spacing = 472.440945

Initializing new database.

Creating layers.

Reading PADS ASCII file body.

*PARTTYPE*

*MISC*

*MISC*

*MISC*

*MISC*

*MISC*

*REUSE*

*TEXT*

*LINES*

*VIA*

*PARTDECAL*

*PARTTYPE*

*PART*

*ROUTE*

Writing routes.

*POUR*

*END*

===============================================================================

ADS layer usage summary:

Layers 1 to 2 are route layers.

LINES:

0 BOARD GEOMETRY - ALL

1 ETCH - TOP

2 ETCH - BOTTOM

20 * Not mapped!

COPPER:

1 ETCH - TOP

2 ETCH - BOTTOM

TEXT:

0 BOARD GEOMETRY - ALL

1 ETCH - TOP

21 * Not mapped!

22 * Not mapped!

23 * Not mapped!

24 * Not mapped!

27 * Not mapped!

DECALS:

0 PACKAGE GEOMETRY - SILKSCREEN_TOP

1 PACKAGE GEOMETRY - SILKSCREEN_TOP

PADS:

0 ETCH - internal_pad_def

1 ETCH - TOP

2 ETCH - BOTTOM

25 * Not mapped!

VIAS:

0 VIA CLASS - internal_pad_def

1 VIA CLASS - TOP

2 VIA CLASS - BOTTOM

WARNING: 19 data objects mapped to the UNUSED class were ignored.

===============================================================================

Creating D:\Allegro\pcbenv\PCMCIA-ReaderV3.brd.

Loading netlist:

D:\Allegro\pcbenv\PCMCIA-ReaderV3.TXT

Writing database.

Closing database.

Translation complete.

Finished reading input file with no errors.

**********Screen Output**********

Creating padstack definitions.

Creating symbols.

... 50 entities converted.

Creating independent data.

... 100 entities converted.

... 150 entities converted.

... 200 entities converted.

... 250 entities converted.

... 300 entities converted.

... 350 entities converted.

... 400 entities converted.

... 450 entities converted.

... 500 entities converted.

... 550 entities converted.

... 600 entities converted.

... 650 entities converted.

... 700 entities converted.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 1455. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 1697. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 1698. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 1699. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2179. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2180. Continuing.

... 750 entities converted.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2408. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2769. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2770. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2788. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2789. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2790. Continuing.

WARNING VOIDs must have same width as their parent SHAPE. Can't create void of shape. iges id 2791. Continuing.

... 800 entities converted.

请高手帮忙!

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:SPB 15.7 安装后 Capture能用,Allegro不能

下一篇:阻抗控制板一般要比非阻抗控制板贵多少?