- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用constraint manager进行等长走线控制

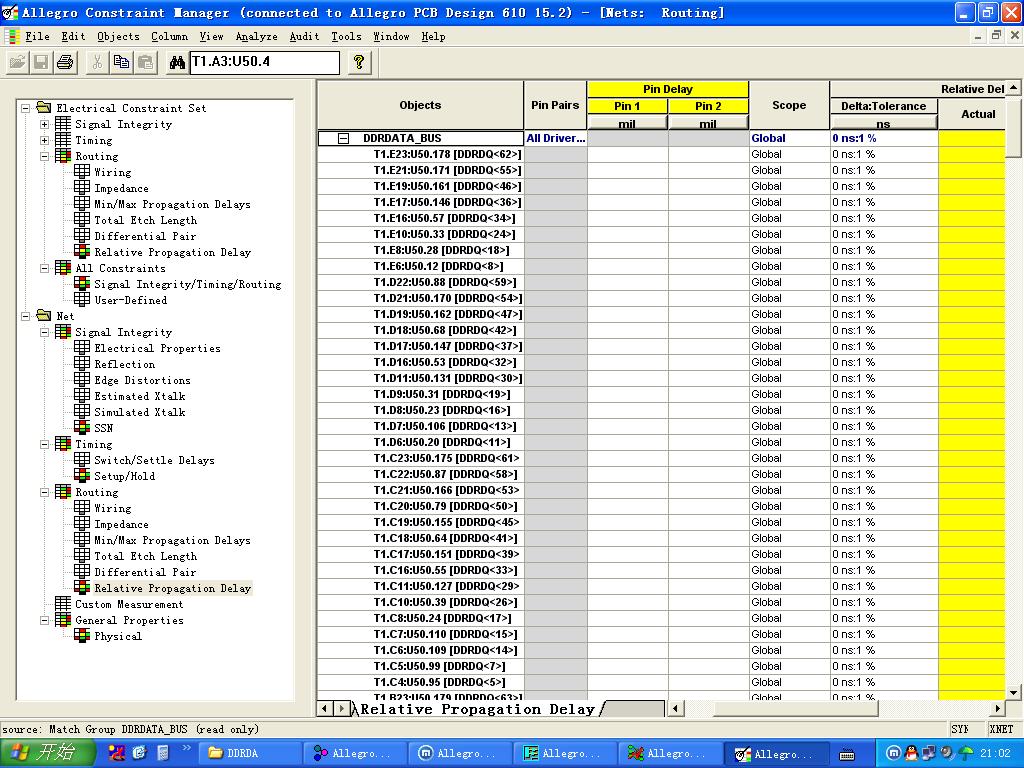

为了走等长线,我先在contraint manager里面设置了Relative Delay,如下图:

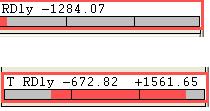

然后走线的时候走边有了这样的提示:

请问上面的RDly是什么意思,其旁边的数字又是代表什么,这是我走第一根线出现的,下面的那个走边还多了一个+1586.85,请问这又是为什么,这是我走另外一根线出现的。诸多不解,请大家赐教,不胜感激!

只有精通了constraint manager才算精通了Allegro,这也是一道坎

我也遇到了同样的问题,怎么解决?

我也想知道呀

盼小编解决

小编的图看不清楚

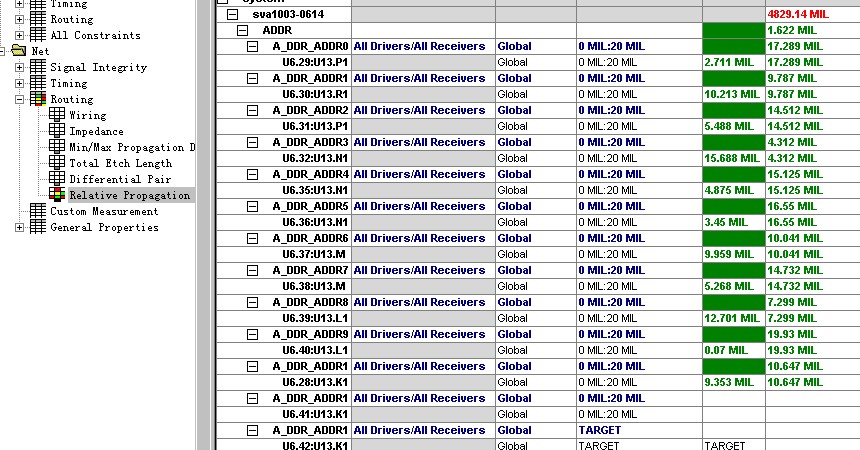

不知道小编选择单位没有,在Delta Tolerance里选择单位后要输入指定线长的规定,如:正负1毫米的误差就输入0 mm:2 mm,最好再选一根作为基准线,在你走线时就会显示那个框,提示他以基准线为标准是负多少还是正多少,如果是显示绿色就是OK了

补充一点,小编的PIN PAIR一栏里没有定义

谢谢楼上的解答,但是我在走第一根的线的时候左边就出现了RDly -1284.07这个东西,请问这是怎么回事,而且我的PIN PAIR一栏是灰色的,定义不了

图看不清的话可以直接点击图打开看。

看来大家都不懂这个constraint manager,你们知不知到为什么要等长,什么信号才会要等长。

我不知道为什么会出现这样的,那应该是饶线是才会出现,其实出现的都是一样的,都是告诉你这根信号在你规定的范围里少了多少(负)或多了多少(正)

如果你PIN PAIR没有定义的话就没有用

经过摸索,我明白是怎么回事了,首先建立PIN PAIR,再建立match group,然后指定一个PIN PAIR为TARGET,

一般系统是默认走第一个Pin pair为Target的,如果不满意系统的指定,也可以在一个Pin Pair的DELTA处右击选择Set as Target。

你可以在建立的match group中,选择the longest pair(即系统选择最长走线作为TARGET,选别的则选的TARGET线不同),然后设定delta中的偏差容忍值,这样,你在画线时就会出现小编贴的走线提示图了。第一幅图是非TARGET线的走线提示图,表示所走线的长度距离最长线还差1284.07mil,第二幅图是TARGET线或者和TARGET线长度非常接近,可以影响到最长线长度的线(一般可能是次长线),含义为比最短的线长了1561.65 ,比最长线短了672.82。

不建立match group怎么行了?

可是等长走线控制,应该在做SCH时候就设定的,可是OrCAD我不知道怎么用,大家有什么好方法吗?

如果在contraint manager设置了,再一次导入网络时候,就会被冲掉。大家有什么好的方法。

等长怎么能在SCH里面控制?楼上的问题其实是A软件的一个BUG,如果原理图不更改网络名,一般是没有问题的。

设计中尽量不要改原理图是最好了。

另外忘了一点,尽量不要用软件自动生成的网络名

问题解决了,多谢朋友!

这个也可以解决啊,把你设好的环境导出来,再把他导进你PCB中就可以了

以下是引用Cdriver_365在2006-4-26 14:10:00的发言:

可是等长走线控制,应该在做SCH时候就设定的,可是OrCAD我不知道怎么用,大家有什么好方法吗?

如果在contraint manager设置了,再一次导入网络时候,就会被冲掉。大家有什么好的方法。

这个也可以解决啊,把你设好的环境导出来,再把他导进你PCB中就可以了

在allegro15.5中,你再试一试.设置好的拓扑结构和规则都会被冲掉.这是15.5的bug.如果是15.2就可以用你说的这个方法.

我還是不太清楚ㄝ

各位大侠,请问下在constrain manager中,设置若干net等长时,能否以两条或n条net的长度的平均值作为target。不胜感激。

不行。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:求助?知道原因的说下 谢谢

下一篇:电脑主板外包