- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请高手进来讨论DRC 问题

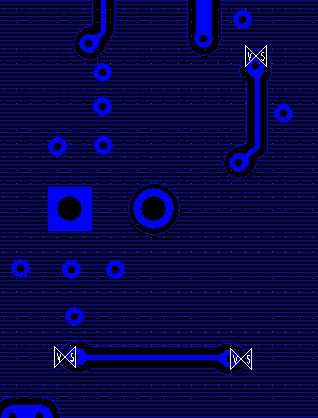

如图所示,本来是已经避开的,但还是有DRC 显示,必须一一去动下

下面是drc信息,为什么会有0.01的差距?我格点是设置为1

LISTING: 1 element(s)

< DRC ERROR >

Class: DRC ERROR CLASS

Subclass: BOTTOM

Origin xy: (2391.00 1048.00)

CONSTRAINT: Shape to Thru Via Spacing

CONSTRAINT SET: DEFAULT

CONSTRAINT TYPE: NET SPACING CONSTRAINTS

Constraint value: 7 MIL

Actual value: 6.99 MIL

- - - - - - - - - - - - - - - - - - - -

Element type: SHAPE

Class: ETCH

Subclass: BOTTOM

Part of Net Name: AGND

- - - - - - - - - - - - - - - - - - - -

Element type: VIA

Class: VIA CLASS

origin-xy: (2391.00 1036.00)

part of net name: VCM

number of connected lines: 2

padstack name: VIA24D12

padstack defined from TOP to BOTTOM

rotation: 0.000 degrees

via is not mirrored

- - - - - - - - - - - - - - - - - - - -

没碰到过.

我也想知道~有遇過此問題的人幫忙解答一下吧....感激不盡

是不是和板子开始设置的单位精度有关系啊?你把精度设置大一些,小数点后5位试试!

我也总是遇到这样的问题

update DRC试试,和格点没有关系

是否是由于单位之间的转换问题造成的呢? 就好像本来是用mil的后来改成了mm,当再使用mil的时候由于小数点保留的位数的差别,就会出现微小的差距。

七楼的说得很对 可以不用管他,也可以重新避让一次

我也没有遇过。

比较常碰见,觉得好像没有什么特定的解决方法,就是有时候铺铜会出现这种情况,单位转换什么的也碰见过

一般如果少的话就手动去调一下,多的话就改一下避让距离的规则,有时候就能好一些,

和grid似乎没有什么关系,感觉出现比较随机

将铜皮变成静态铜,让后在变成动态铜就没问题了