- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

OrCAD不能生成网表,由于CPU芯片原理图分成了五个部分,网表时不能正确识别

生成网表时,报如下错误:

#18 Warning [ALG0016] Part Name "RESISTOR DIP 4_0_R_SMT8_0-0603X4_NC" is renamed to "RESISTOR DIP 4_0_R_SMT8_0-060_1".

#19 Warning [ALG0016] Part Name "RESISTOR DIP 4_0_R_SMT8_330-0603X4" is renamed to "RESISTOR DIP 4_0_R_SMT8_330-060".

#20 Warning [ALG0016] Part Name "SW SLIDE-SPDT_2_SLIDE_SW_SWICH_JACK" is renamed to "SW SLIDE-SPDT_2_SLIDE_SW_SWICH_".

#21 Warning [ALG0016] Part Name "88AP303-A1-BGF2C624-TN22_8_VFBGA409_88AP303-A1-BGF2C624-TN22" is renamed to "88AP303-A1-BGF2C624-TN22_8_VFBG".

#22 Error [ALG0014] Conflicting values of part name found on different sections of "U1".

Conflicting values: 88AP303-A1-BGF2C624-TN22_8_VFBGA409_88AP303-A1-BGF2C624-TN22 & 88AP303-A1-BGF2C624-TN22_1_VFBGA409_88AP303-A1-BGF2C624-TN22

roperty values of "Device","PCB FootPrint" and "Value" should be identical

on all sections of the part.

#23 Error [ALG0014] Conflicting values of part name found on different sections of "U1".

Conflicting values: 88AP303-A

1-BGF2C624-TN22_8_VFBGA409_88AP303-A1-BGF2C624-TN22 & 88AP303-A1-BGF2C624-TN22_1_VFBGA409_88AP303-A1-BGF2C624-TN22

roperty values of "Device","PCB FootPrint" and "Value" should be identical

on all sections of the part.

#24 Error [ALG0014] Conflicting values of part name found on different sections of "U1".

Conflicting values: 88AP303-A1-BGF2C624-TN22_8_VFBGA409_88AP303-A1-BGF2C624-TN22 & 88AP303-A1-BGF2C624-TN22_1_VFBGA409_88AP303-A1-BGF2C624-TN22

roperty values of "Device","PCB FootPrint" and "Value" should be identical

on all sections of the part.

#25 Error [ALG0014] Conflicting values of part name found on different sections of "U1".

Conflicting values: 88AP303-A1-BGF2C624-TN22_8_VFBGA409_88AP303-A1-BGF2C624-TN22 & 88AP303-A1-BGF2C624-TN22_9_VFBGA409_88AP303-A1-BGF2C624-TN22

roperty values of "Device","PCB FootPrint" and "Value" should be identical

on all sections of the part.

#26 Aborting Netlisting... Please correct the above errors and retry.

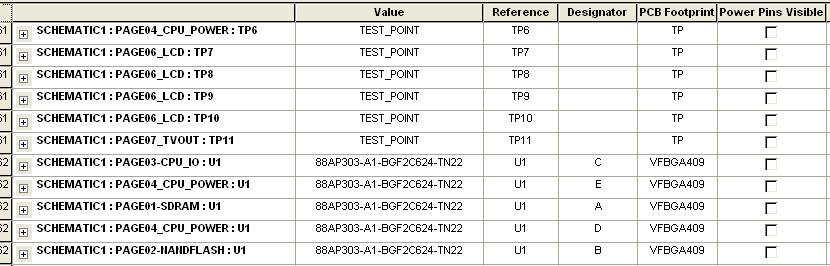

这样不能正常生成网表,这U1这个器件分成了五个部分,U1A,U1B,....,U1E等部分,属性栏检查了,如下,应该没有问题:

我重新设计了一个简单的类似器件,分成3个部分,可以正常生成网表,属性栏跟上面的图是一样的。感觉这个问题比较奇怪,是不是软件出现问题了。

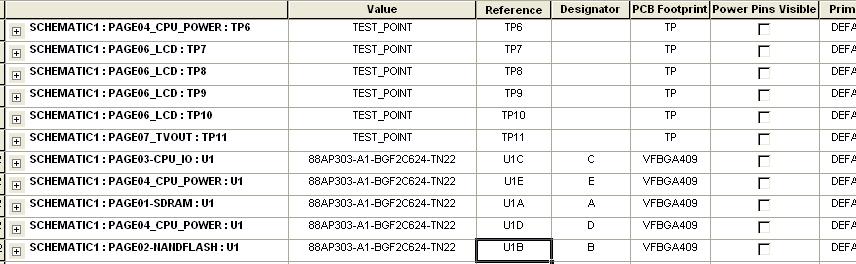

上面的U1,把他改成如下形式时,就可以正常生成网表,不会报错!但导入Allegro时,会出现错误,被分成了五个器件,能到处一个器件放下到PCB板上,但没有网络。

请问那位高手可碰到过类似的问题?或有什么好的建议?谢谢

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:关于盲埋孔的问题

下一篇:如下两种丝印如何调整?