- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电源层请问一般是用负片还是正片

庸手一般都出正片,有的都没听说过负片。

混合电源层用正片,独立的用负片

负片好,数据量小,不宜出错

電源層用負片好一點吧

能否给个确定的说法,我现在做一个四层板,模拟地和数字地一层,四组电源作一层,我想知道如何去分割内电层呢?:)我用split plane命令,结果说只能对于正片进行操作,而我开始wizard时就采用默认的参数,内层都用负片了。现在该怎么办?:)可不可以用填充实心shape的方法来做内电层?:)谢谢指教!

能否有高手出来指教一二.第一次用Allegro做多层板,有些概念很模糊。

我做的是四层板 ,TOP,Layer2,Layer3,Bottom。定义 Layer2,Layer3 均为Negative Plane.

决定Layer2 包含 AGND,DGND两部分, Layer3 包含 A15V,A-15V,D6.5V,D5V.

已经完成布线,AGND,DGND 以及各电源均已打好VIA ,只需要在内层中相连即可。

那么,在对Layer2 和Layer3操作时,我是否是应该根据 help 文档中“Creating a Negative Plane”的操作步骤,在ETCH类中执行Add->Shapes->Solid Fill 操作,将不同的网络分划在一个 shape中就可以?有无其他特殊要求,比如焊盘是否一定要有flash?

内层用SHAPE连起来即可,当然要给SHAPE加上NET属性。

然后要给VIA定义FLASH和ANTI PAD。否则就全短路啦。

谢谢,VIA的Flash 和ANTI PAD我都加了,但是有些通孔焊盘的thermal relief我没用Flash,就用普通circle会不会有问题?

还有,问一个技巧问题,如果同时显示所有的GNDD,GNDA 网络上的pad和VIA,还能区分出来?我板上的这两个net的pad和VIA互相交错,我在add shape是没办法区分。

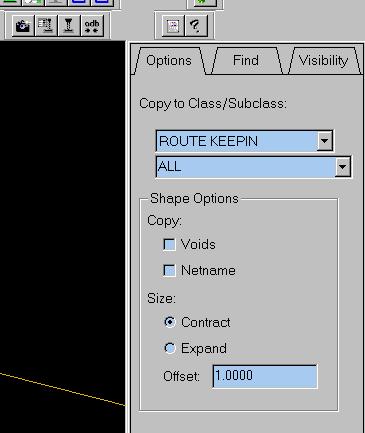

1,首先选取EDIT-》Z-COPY命令添加routekeepin,offset设为1mm,参数设置如下:

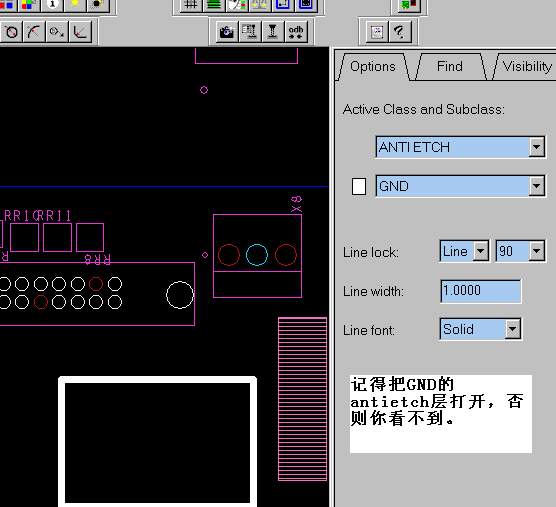

2,add-》line命令参数如下:在GND层勾画出数字地和模拟地分区,注意不能有缺口,保证完全分开。

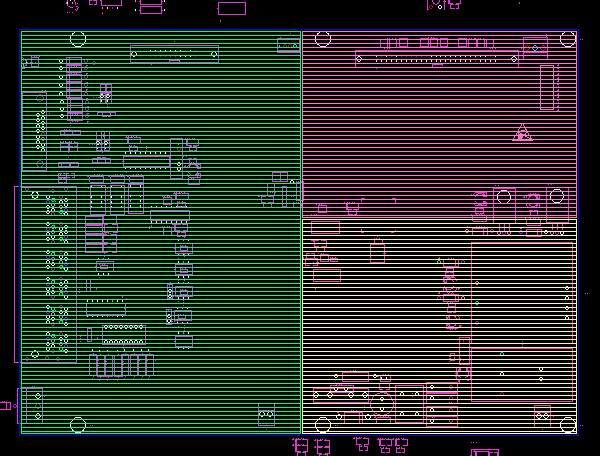

3,隔离区画完之后,先看看我提供的例子:

To be continued!

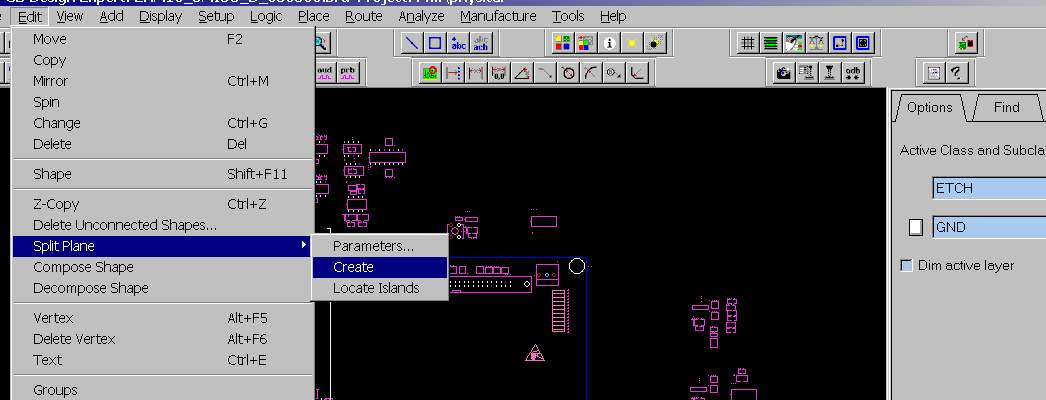

4,选取如下命令,注意右边打开相应的层

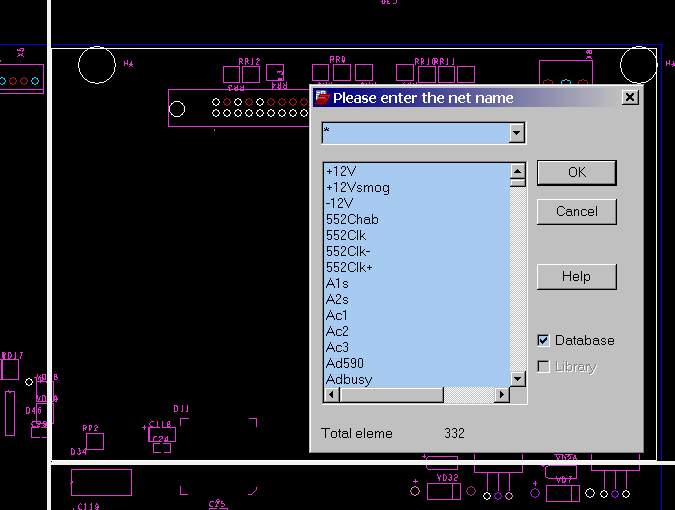

5,跳出如下对话框时,选择相应的GND即可。

6,关闭Antietch层显示,分布高亮显示三个不同的GND显示如下:That's all

靠!好累,中午也没休息,总算答复完了。

还有,电源层与此类似,自己玩吧!

不同的网络的表示可以用HILIGHTE,选不同的颜色将网络点亮。

焊盘设置FLASH是为了内层导通,如果不需要接电源或地的话,不设也没关系。

哇塞!向你致以崇高敬意!真是好“代表” :)谢谢了,我认真研读一把!

原来高亮一个网络后可以修改颜色再来点亮别的网络的,又明白一个东东!

thanks you all!

to -- 水云

内层如果是负片的话不用做AUTO VOID .

to kuro96 :

如果不做auto void,虽然split plane给不同的网络添加了shape,但是对via和hole都没有避让,也没有产生thermal relief 连接相应网络啊,不过看上去的效果就是和上面最后一张图所示,分化成两个不同区域,全部被覆盖.

DRC检查报错:

ERROR IN NET name = D6.5V

Ratsnest lines are out of date.

Error cannot be fixed.

这是什么意思?另外,在改pad时,我仅仅将design里各pad的VCC,GND两个内层thermal relief改为flash,然后update to design,Drill hole size is equal or larger than smallest pad size.

Pad will be drilled away.我看过drill hole size,根本就比pad size 任何一个参数都小很多。这是什么原因呢?奇怪啊!

就是这样的,不用避让。

呵呵,谢谢michael1998,我终于可以进行内电层分割了,不过那个z-copy是干吗用的?

z-copy用于复制shape.

不错

好!頂!

z-copy用于生成限制走线的route keepin 区域 走线走出此区域会产生drc

一般来说,pcb板量产时需要夹边上件,一般mother board的route keepin区域应该距板边20mil

对于route keepin 我有不同意见。它主要是防止走线因到达板边后与金属接触而短路,我是这么理解的,当然,可能还有别的用处。

对于,夹边上件,应该是package keepin区域,大约160mil(4mm)

负片!

以下是引用eric57在2004-6-7 16:12:00的发言:

对于route keepin 我有不同意见。它主要是防止走线因到达板边后与金属接触而短路,我是这么理解的,当然,可能还有别的用处。

对于,夹边上件,应该是package keepin区域,大约160mil(4mm)

不是到达板边短路,而是担心切板的时候因为变形而断裂。

刚开始学allegro,顶一个

解释的真麻烦啊!

route keepin看名字就知道是让线走到里面的区域,你关它是做什么的啊,和route keepout一样,是不允许线走到里面的区域。

da bu chu zi bei ju le