- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于晶振同时给DSP 和FPGA同时提供时钟的问题

录入:edatop.com 点击:

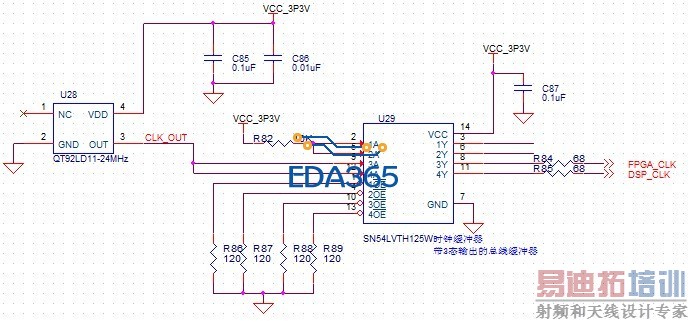

上面是这个纠结的原理图,其中LVTH125芯片是一个bus buffer,接到了这里有任何意义吗?9脚和12脚输入晶振的clock然后下拉电阻接地,表示3A 3Y 连通4A4Y连通,然后接出去给dsp和FPGA供给时钟。这样是出于什么考虑呢?

提供驱动?我能找到这个晶振的最大负载15pF // 10kohms,如何知道dsp是否过负载呢?

提供驱动?我能找到这个晶振的最大负载15pF // 10kohms,如何知道dsp是否过负载呢?

提高晶振的负载能力吧

还有公用一个晶振,估计有时钟同步的意思。

要求不高可以2个芯片直接接一个晶振的,我们测试过我们自己研发的的ASIC 8个芯片公用一个有源晶振能正常工作,并且量产了没什么问题。

用时钟分配器就可以了。

的确是为了时钟同步,但是提高晶振负载能力这一项,我有个问题。

一下是这几个的参数

晶振的output load :

15pF // 10kohms

(30pF max. for F ≤ 50MHz)我用的24M,因此最大可以负载30pf

dsp的datasheet中提到输入电容 15pf

FPGA 的datasheet中提到clock pin capacitance 12pf

请问我可以不为了提高负载能力而专门加这个lvth125器件吗?

老师

使用时钟分配器的目的是什么呢?

是为了提高负载能力吗?

晶振的output load :

15pF // 10kohms

(30pF max. for F ≤ 50MHz)我用的24M,因此最大可以负载30pf

dsp的datasheet中提到输入电容 15pf

FPGA 的datasheet中提到clock pin capacitance 12pf

我感觉上面的数据可以不为负载能力考虑

是为了去掉因为一个时钟线分出两根线走T形结构导致的信号完整性问题吗?

我也不用电平转换之类的。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>