- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

怕黏锡的做法?

录入:edatop.com 点击:

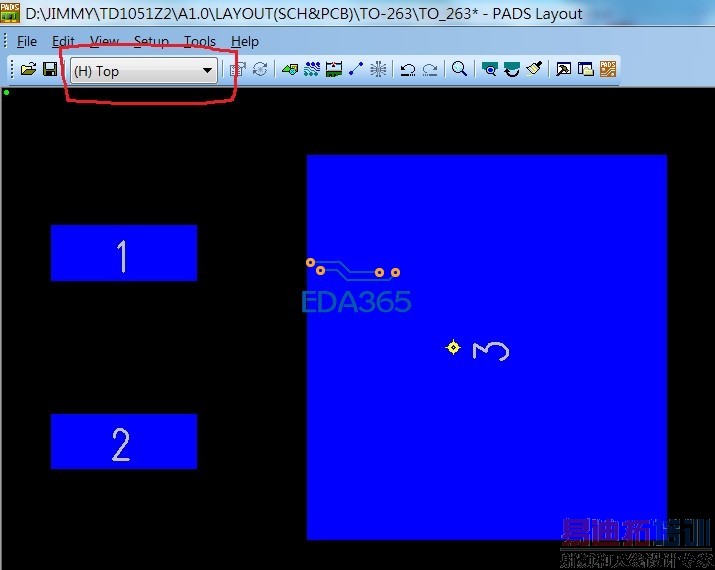

最近有个TO-263的封装,我自己手工建立,

但是就是无聊从LP Wizard调出TO-263封装,

先声明这个封装的3号脚的PAD比较大,

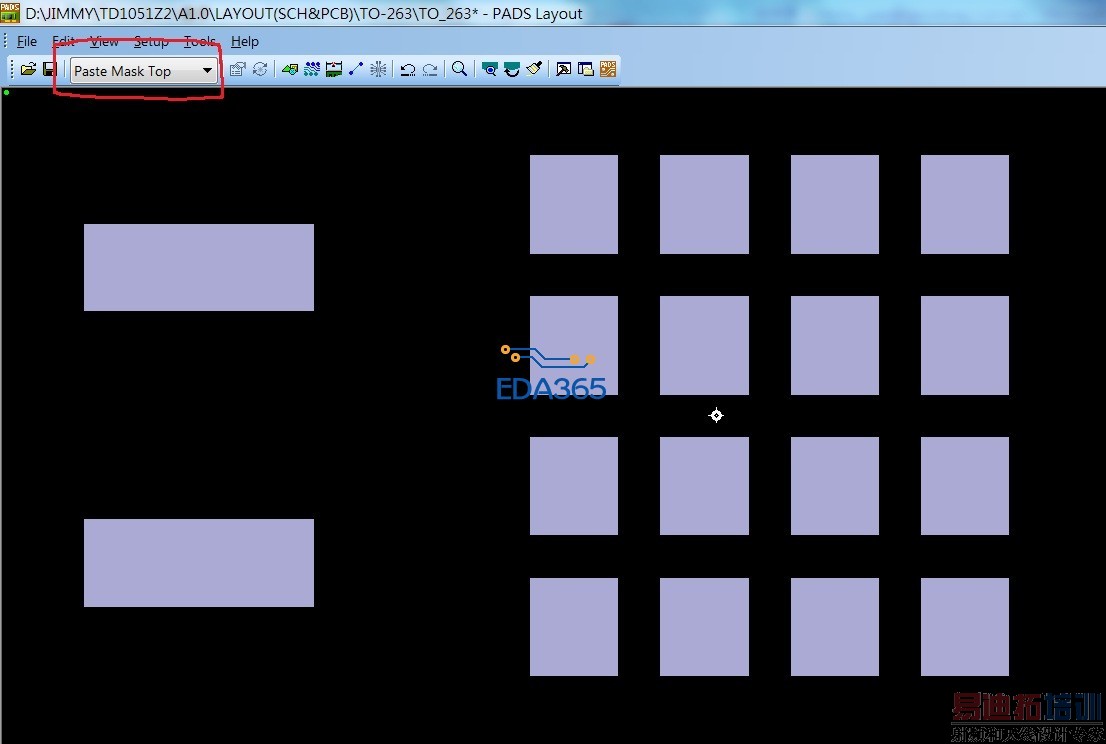

发现这个软件建立出来的Pastemask Top非常奇怪,

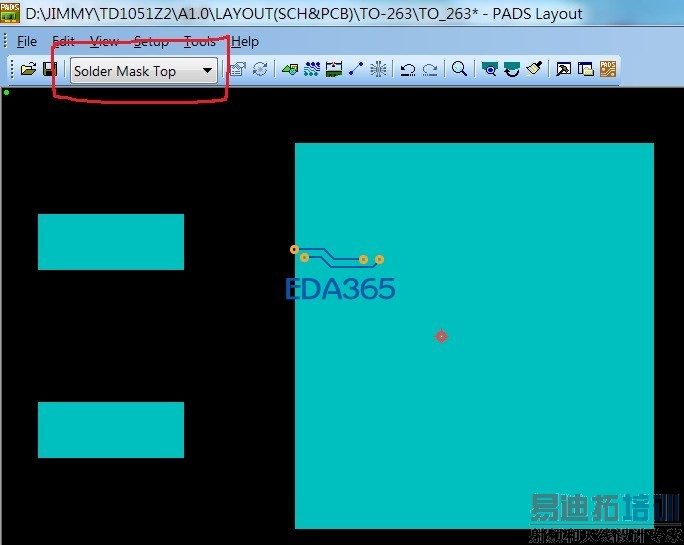

Pastemask Top与Soldermask Top在3号脚,居然不一样!

感觉做成这样,是怕让过锡炉,不会黏锡,

不知道,我的理解是否正确?

但是,大家在制作过大的PAD, 怕黏锡也会这样做吗?

各位前辈,可否给点建议?

焊盘太大,锡膏上的太多,元件容易浮起,容易偏移,容易产生锡珠。

在之前的公司,这种焊盘开钢网的时候都会出具说明这种大焊盘需要做防锡珠处理,钢网厂就知道要做成多个小焊盘的形式。

问一下黏锡是什么现象?

个人觉得钢网修正事情应该留给焊接厂,设计师就1:1把PASTE窗开好,让厂子的人根据他们自己的工艺再修正

我的问题是这个封装的soldermask_top和pastemask_top为何做成不一样

跟你讲的那个没关系您没搞懂我问的

关注,一直以来钢网都这么开,有时也想过为什么,但都一闪而过

我同事是建议soldermask_top和soldermask_bottom做成一样把线路图的三号脚,拆成318,然后三号脚会有16个PAD,但是 我觉得他的方法好麻烦,还是觉得 建立我上面的图 那种封装比较好唉

开得太大中间会堆一堆锡的

谢谢大家的指教

我心里大概有个底

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:叠层问题,请大师指导

下一篇:关于晶振同时给DSP 和FPGA同时提供时钟的问题

射频和天线工程师培训课程详情>>