- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于EPM1240的SDRAM控制器的设计

摘要:SDRAM的读写逻辑复杂,最高时钟频率达100 MHz以上,普通单片机无法实现复杂的SDRAM控制操作,复杂可编程逻辑器件CPLD具有编程方便,集成度高,速度快,价格低等优点。因此选用CPLD设计SDRAM接口控制模块,简化主机对SDRAM的读写控制。通过设计基于CPLD的SDRAM控制器接口,可以在STM系列、ARM系列、STC系列等单片机和DSP等微处理器的外部连接SDRAM,增加系统的存储空间。

关键词:SDRAM;接口;Verilog;CPLD

数据采集处理技术是现代信号处理的基础,广泛应用于雷达、声纳、软件无线电、瞬态信号测试等领域。随着信息科学的飞速发展,人们面临的信号处理任务越来越繁重,对数据采集处理系统的要求也越来越高。近年来复杂可编程逻辑器件(Complex Programable Logic Dev ice,CPLD)由于其设计灵活性、更强的适应性及可重构性,结合同步动态随机访问存储器(Synchronous Dynamic Random Access Memory,SDRAM)的高速、大容量、价格优势,在设计高速实时数据采集系统时受到了广泛的关注。SDRAM(同步动态随机访问存储器)具有价格低廉、密度高、数据读写速度快的优点,从而成为数据缓存的首选存储介质。

1 SDRAM的基本操作

SDRAM称为同步动态随机存储器,同步是指其时钟频率与CPU前端总线的系统时钟频率相同,SDRAM可以使所有的输入输出信号保持与系统时钟同步,并且内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据的读写。由于SDRAM为了提高存储容量,采用硅片电容来存储信息,随着时间的推移,必须给电容重新充电和刷新来保持电容里的数据信息。

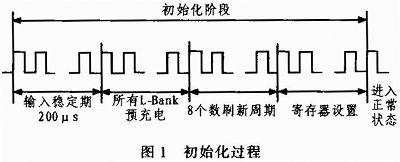

在对SDRAM进行存取数据操作之前,首先要对其初始化,即设置SDRAM的普通模式寄存器和扩展模式寄存器,确定SDRAM的工作方式,这些设置包括突发长度、突发类型、CAS潜伏期和工作模式的设置。在SDRAM芯片内部有一个逻辑控制单元,并且有一个模式寄存器为其提供控制参数。因此,每次开机时SDRAM都要先对这个控制逻辑核心进行初始化。初始化过程如图1所示。

1.1 模式寄存器的设置

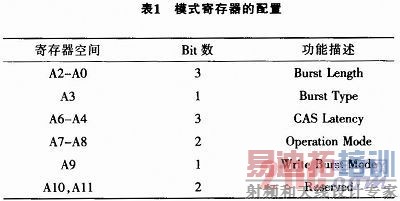

Mode Register Set:模式寄存器设置,是指对SDRAM的工作方式做一定义,对寄存器的设置,可以在每次系统启动时,也可以在每次存取之间进行,当SDRAM掉电时,系统重新启动后必须重写模式寄存器。其空间安排如下表1所示:

Burst Length:决定当接受到一个读写信号时可以读取的最大的列数目,对于连续读取模式,其值可以为1,2,4,8或整页(full page),当为隔行读取模式是,其值为1,2,4,8。

Burst Type:决定读取模式为连续方式还是隔行方式。

CAS Latency:决定当一个读信号有效到第一个数值在数据线上有效时之间的间隔延迟时间,延迟时间可以设定为1,2或3个时钟周期。例如:如果延迟时间为m,读信号在n时刻有效,那么数据将在第m+n个时钟信号有效,如果相应的读取时间适合的话,而在m+n-1时刻数据线传送数据。

Operation Mode:A7-A8表示操作的模式。

Write Burst Mode:当A9=0时,有A0-A2决定的Burst Length适合于读和写两种操作。而当A9=1时,Write只能读取单一的单元,而不能支持块操作。

Reserved:A10,A11是保留位,为以后的扩展使用。 [p]

1.2 预充电

由于SDRAM的寻址具有独占性,所以在进行完读写操作后,如果要对同一L-Bank的另一行进行寻址,就要将原来有效(工作)的行关闭,重新发送行/列地址。L-Bank关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。预充电可以通过命令控制,也可以通过辅助设定让芯片在每次读写操作之后自动进行预充电。实际上,预充电是一种对工作行中所有存储体进行数据重写,并对行地址进行复位,同时释放S-AMP(重新加入比较电压,一般是电容电压的1/2,以帮助判断读取数据的逻辑电平,因为S-AMP是通过一个参考电压与存储体位线电压的比较来判断逻辑值的),以准备新行的工作。具体而言,就是将S-AMP中的数据回写,即使是没有工作过的存储体也会因行选通而使存储电容受到干扰,所以也需要S-AMP进行读后重写。此时,电容的电量(或者说其产生的电压)将是判断逻辑状态的依据(读取时也需要),为此要设定一个临界值,一般为电容电量的1/2,超过它的为逻辑1,进行重写,否则为逻辑0,不进行重写(等于放电)。为此,现在基本都将电容的另一端接入一个指定的电压(即1/2电容电压),而不是接地,以帮助重写时的比较与判断。

1.3 刷新

SDRAM之所以称为同步动态随机存储器,就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是SDRAM最重要的操作。刷新操作与预充电中重写的操作一样,都是用S-AMP先读再写。进行预充电操作还要进行刷新的原因:因为预充电是对一个或所有L-Bank中的工作行操作,并且是不定期的,而刷新则是有固定的周期,依次对所有行进行操作,以保留那些久久没经历重写的存储体中的数据。但与所有L-Bank预充电不同的是,这里的行是指所有L-Bank中地址相同的行,而预充电中各L-Bank中的工作行地址并不是一定是相同的。

目前公认的标准是,存储体中电容的数据有效保存期上限是64 ms,也就是说每一行刷新的循环周期是64 ms,这样刷新速度就是:行数量/64 ms。内存规格有4096Refresh Cyeles/64 ms或8192 Refresh Cycles/64 ms的标识,这里的4096与8192就代表这个芯片中每个L-Bank的行数。刷新命令一次对一行有效,发送间隔也是随总行数而变化,4096行时为0.625 ps,8192行时就为7.812 5 ps。刷新操作分为两种:自动刷新(Auto Refresh,简称AR)与自刷新(Self Refresh,简称SR)。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。

2 系统硬件设计

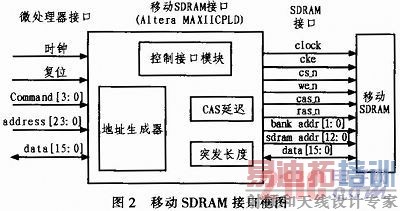

移动SDRAM接口设计包括四个主要模块,如图2所示,即控制接口模块、CAS延迟、突发长度以及地址生成器。下面对这些模块进行简要介绍。

2.1 控制接口模块

控制接口模块内部是有限状态机(Finite-State Machine,FSM),有限状态机解释来自微处理器的输入,把相应的命令和符合时序要求的地址发送给移动SDRAM设备,然后,移动SDRAM设备进入相应的状态,执行命令。

有限状态机会综合考虑存储器的时序要求,以正确的顺序产生各种操作指令,在发出操作指令之前,控制器首先会给出一个读取使能信号,从数据输入输出缓存模块的地址指令中读取地址指令。控制接口模块解码并寄存主机发送的命令,把解码后的空闲、写、读、刷新、充电和模式设置命令和地址信号送给命令模块。状态机的状态转换如图3所示。

2.2 CAS延迟模块

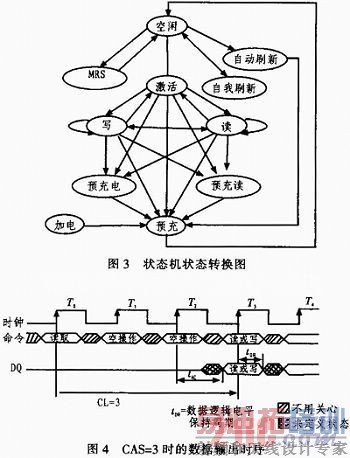

CAS延迟通过模式寄存器配置,CAS延迟模块的实质是2位递增计数器,这一计数器监视CAS延时时钟周期数。它表示读命令和第一个输出数据之间延迟的时钟周期数,延时时钟周期数可以是二或三个时钟周期。图4分别给出CAS=3时的数据输出时序。

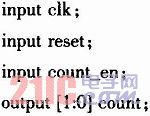

2位递增计数器的输入输出如下:

clk是输入的时钟信号来自微控制器,reset输入的异步复位信号,count_en输入的计数使能信号,count输出的CAS延迟数。系统不复位的情况下在计数使能有效时当时钟上升沿到来CAS延迟增加。 [p]

2.3 突发长度模块

突发长度也使在模式寄存器中设置的,它的内部实质是4位递增计数器,这一计数器监视读写突发工作时的时钟周期数,原理与2位递增计数器相同。

突发长度可以是1、2、4或者8,突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度。

2.4 地址转换模块

地址发生器将微处理器提供的地址按照要求的格式映射到移动SDRAM设备上。命令模块接收控制接口模块输入的解码后的命令和刷新控制单元发出的刷新请求命令,产生合适的SDRAM操作命令。

该模块包含一个简单的仲裁逻辑单元,仲裁主接口和刷新单元发出的命令,刷新请求的优先级最高。当刷新单元和主接口同时发出命令时,仲裁单元挂起主接口的命令直到刷新操作执行完毕;若主接口发出的命令正在执行时,仲裁单元挂起刷新命令直至正在处理的操作执行结束。仲裁单元接收控制接口模块发出的命令后,命令产生单元根据接收到的命令产生合适的SDRAM控制信号。命令产生单元基于三个移位寄存器产生正确的时序:第一个寄存器控制SDRAM激活命令的时序;第二个寄存器控制SDRAM读写时的时序;第3个用于产生命令延时,以便决定所请求的命令是否执行完毕。它根据状态分别产生块和行列地址,并传送到移动SDRAM设备上。

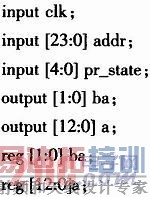

地址发生器的输入输出如下:

clk是系统的主时钟输入,addr是输入的地址信号,pr_state是输入的当前状态,这3个信号均由微控制器提供。地址发生器接收来自微控制器的命令,把命令转换成SDRAM能够理解的状态信号,地址发生器根据状态信号产生相应的地址选择SDRAM的行或列进行操作。

3 系统的设计与实现

选择ALTERA公司MAXⅡ系列的EPM1240芯片,用CPLD方式实现SDRAM接口。接口仿真时序图如图5所示。

SDRAM接口仿真波形图如图5所示,其中sd_clk_97为操作SDRAM的时钟,sd_cke_98,sd_csn_99,sd_casn_103,sd_rasn_105,sd_wen_106分别为时钟使能信号,片选信号,列选通信号,行选通信号和读写使能信号。sd_ba是SDRAM的2位Bank地址线,sd_a_是SDRAM的13根地址线。data为SDRAM的16位输入/输出双向数据线。

4 结论

在SDRAM的接口设计中,刷新的实现一直是一个关键问题。选用CPLD产生控制SDRAM的时序,实现对SDRAM的各种操作。应用Verilog语言和QuartusⅡ软件实现了SDRAM的接口设计,在QuartusⅡ软件环境下模拟了STM32系列单片机对SDRAM的读写操作时序,读写速度达到100MHz,可以在STM32系列单片机扩展64 MBit的SDRAM,其中SDRAM的地址线为13根(行地址线13根,列地址线9根),Bank地址线2根,数据线16根。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...