- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于NIOS II的导航系统平台的设计

目前广泛应用的MIMU/GPS组合导航系统的实现形式,依应用领域的不同而复杂多样,但是导航计算机板卡负责的工作则相对固定,其主要包括:采集各路传感器输入信号;滤波、融合计算;将计算结果输送给机电控制子系统;提供各种人机交互接口,如LCD,键盘等。

长期以来,针对各种应用领域或相同领域的不同场合,由于对控制计算能力、接口电路数据吞吐能力等要求的差异,我们习惯于把功能相对固定的导航计算机子系统设计成不同的实现形式,这就造成了对硬件重复研发,相应软件重复调整等低效率现状。

SOPC(System On Programmable Chip)技术是Altera公司提出的一种灵活高效的SOC解决方案。它的宗旨是将处理器、存储器、I/O口、硬件协处理器或加速器、一般的用户逻辑等系统的设计需要的功能模块都集成到一个FPGA芯片里,构建一个可编程的片上系统。它具有硬件上灵活裁剪、扩充和在线升级的优点,而且市场上有丰富的IP 核资源可选,能成功地解决上述问题。

1.组合导航系统硬件电路的实现

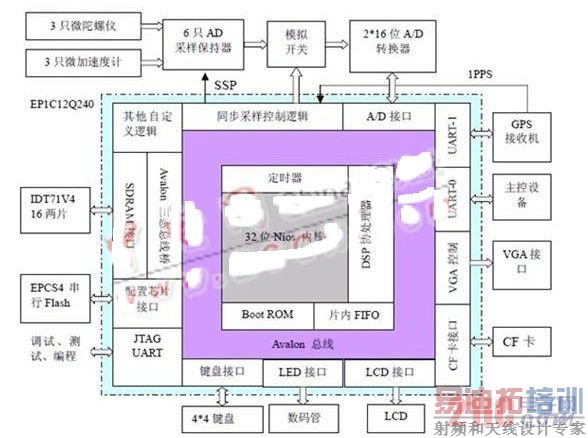

硬件框图如图1所示,它主要包括以Nios处理器为主体的片内逻辑(图中虚线包围部分,下文简称片内逻辑)、MIMU与GPS数据采集电路和人机交互接口电路三个部分组成。

1.1片内逻辑的设计

本文采用了Altera公司Cyclone系列FPGA EP1C12Q240、NIOS软核处理器及其开发和仿真工具(包括 SOPC Builder,DSP Builder,Simulink,Quatus II等)。在设计中利用的IP核里,比如Nios核,片内Boot ROM,用于FIFO的片内双口RAM,定时器,Avalon片上总线,Avalon三态总线桥,SDRAM接口,JTAG UART等都来自SOPC Builder软件,在此不必赘述。下面重点讨论其他IP核及其接口电路的设计和功用。

图 1 基于Nios的SOPC组合导航系统设计框图

6 DSP协处理器 通过定制一些传统的DSP运算指令或反复出现的计算密集型算法指令,来硬件加速CPU的处理能力。IP核可以通过硬件描述语言自己编写,也可以借助Simulink和DSP Builder来辅助实现。

7 UART 基于RS232通信协议的串行通路接口。UART-0负责传递主控设备的命令(如复位、初始化等)、输入主控设备提供的电子地图的库信息,输出处理结果等。UART-1则负责导入GPS OEM板的数据。该IP核来自于SOPC Builder软件。

8 A/D接口 除了片选信号,A/D接口时序基本遵循SPI协议,因此选用了SOPC中相应的IP, 而对于片选信号,在系统中额外添加一个通用I/O口来控制之。这样每次对A/D的操作分两步进行:先置低GPIO,再进行SPI操作。

9 同步采样控制逻辑 负责控制MIMU和GPS信号的同步采集,为数据融合提供准确的输入。该IP核由设计者自行编制,详述请见MIMU和GPS信号采集系统的设计部分。

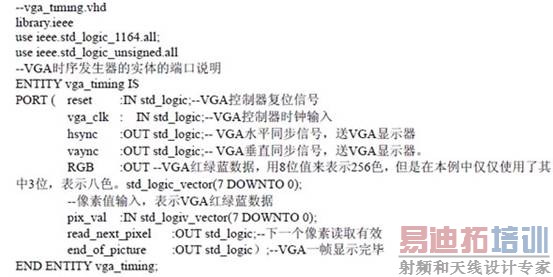

10 VGA控制 基于Avalon流模式的VGA控制器。它主要由VGA时序发生器,FIFO存储器,Avalon流模式接口组成。该IP由设计者用VHDL语言自行编制,人机接口部分将详述之。

11 ATA桥 连接CF卡,保存电子地图信息库、中英文字符点阵库等海量信息。该IP核来自于SOPC Builder软件。

12 GPIO 最常规的外设控制接口,本系统的LCD、LED、键盘都是采用该接口进行连接,时序上的驱动控制则是由软件实现的。该IP核来自于SOPC Builder软件。

13 ASMI EPCS4系列配置芯片的专门接口。该IP核来自于SOPC Builder软件。与之相连的Flash存贮空间中有如下内容:一部分是FPGA的配置文件。另一部分作为常规程序存储器用。采用此方案可以省去片外专门的程序存储Flash,充分利用了配置芯片的资源。由于串行器件的带宽限制,我们可以通过将主程序装载入SDRAM中运行来提高程序的运行速度。

1.2 MIMU和GPS信号采集系统的设计

MIMU的信号采集工作由微型惯性测量组合、采样/保持器AD1154、多路开关MAX4540、A/D 转换器完成;而GPS的信号采集工作则主要由GPS接收机完成。接收机采用了Jupiter OEM 板,可输出位置、速度、伪距、伪距率、载波相位、卫星星历等数据。系统启动期间,主控设备通过UART-0向片上逻辑发送命令并获取信息反馈,对系统导航参数进行初始化;接收的初始化数据可由片上逻辑的UART-1传递给GPS接收机,以实现GPS的快速初始化和快速锁定卫星.

我们所讨论的MIMU和GPS信号的同步,是指需要同步的两个数据源在原始信息更新时刻对齐,而不是在经过计算或A/D转换延时等不同通信路径传输后,在输出结果的时刻对齐。GPS接收机解码转换后输出的秒同步脉冲(1PPS,每秒一个脉冲)是与UTC秒点对齐的。接收机严格地在每个1PPS脉冲边沿进行一次伪距、伪距变化率、载波相位、GPS 标准授时、定位等测量,其脉冲沿为GPS数据更新时刻。我们把1PPS脉冲接入FPGA中,由同步采样控制逻辑保证脉冲到来的同时产生一个SSP(同步采样脉冲,synchronous sampling pulse),实现MIMU和GPS数据在整秒时刻同步。当然,MIMU数据更新率远小于1秒,我们可以把1PPS脉冲作为FPGA内部的1秒定时器的标准同步触发时刻,通过逻辑倍频产生相应频率的SSP输出。在GPS信号丢失的情况下,FPGA内部的秒定时器则作为MIMU采样信号的时基标准。

1.3人机交互接口的设计

七段数码管负责标识系统的工作状态;而键盘除了作为初始化参数输入的备用接口外,还可以负责切换LCD、VGA显示器等的显示模式;液晶屏则相应地显示输入与输出的导航参数;VGA接口形象的输出电子地图背景、车辆当前位置及运行轨迹等信息。

excalibur.h 头文件定义了七段数码管、按键数据结构指针na_seven_seg_pio 和na_button_pio通过对指针所指PIO数据结构内的np_piodata数据寄存器操作,来让数码管显示特定的字符或判断是否有按键按下,以及是哪个按键。

本文采用型号Optrex 16027的LCD屏,头文件pio_lcd16027.h定义了九个控制子程序,通过这些程序完成对LCD的控制。标准VGA画面大小是640*480,每秒60帧左右。像素时钟高达25.175MHZ。如果每个点都由Nios软件扫描实现,那么在40ns的间隔内,最多能让共作在50MHZ的CPU执行两条指令。所以,我们采用DMA控制器在流模式VGA控制器和SRAM之间建立一条DMA传送通道,让硬件完成像素信息的自动读取,缓解了CPU的工作压力。VGA时序发生器的设计源程序由VHDL语言实现,下面是部分示意代码:

2.系统工作原理

系统上电后,串行配置器件EPCS4配置FPGA;然后NIIOS启动,运行片内ROM中的Bootloader。Bootloader根据选择端的控制选择工作模式,模式分为两种:调试模式和运行模式。在调试模式下,Bootloader启动GERMS监控程序,我们可以对系统进行开发调试。在运行模式下,Bootloader将EPCS4中存储的主程序装载到SRAM中全速运行。然后,程序指针复位指向SRAM中的系统主程序。主程序先初始化并配置系统,然后开始正常工作。

3.软件设计

由于本控制系统架构庞大,我们在软件设计时使用实时操作系统microC/OS作为软件内核。该操作系统具有内核小,代码公开等优点,而且Altera公司提供了关于此系统移植方面比较详细的技术文档,操作起来简单易行。系统软件分为三个层次设计:一、驱动层。主要包括了UART驱动,LED驱动,键盘驱动,LCD驱动,VGA驱动,SPI总线设备驱动等等。二、内核层。包括系统任务和内核调度。三、应用层。

任务主要有数据采集任务,数据融合任务,数据滤波任务,导航计算任务,显示任务等。其中还有一些用于控制管理性质的任务,包括错误捕捉任务及其相应的处理方程序等。

系统的核心是操作系统的内核调度,负责整个软件的运作。系统相关的层面是以任务为单位的系统模块,这些任务模块负责市实现导航系统的正常运行,负责系统模块的配置控制和差错检测,响应处理用户的操作。硬件相关的层面以驱动任务为单位,它们作为操作系统和硬件系统中介,直接负责对硬件设备的驱动控制。软件分层封装,用任务调度的方法来实现,可以提高软件设计的效率,降低设计风险,利于移植和升级。

4.结论

NIOS符合工业技术的潮流,即硬件设计软件化。此设计方法可以对硬件做全面细致的模拟仿真,减少硬件设计的错误,有效降低了开发成本,增强了产品的竞争力。而且由于它属于单片解决方案,不仅提高系统的鲁棒性,还可以有效地保护开发者的知识产权。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:LED

驱动电源设计

下一篇:什么是FPGA、SOC、SOPC、DSP?