- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于 CPLD EPM570T100C5的通用直流调速模块设计

1 系统设计

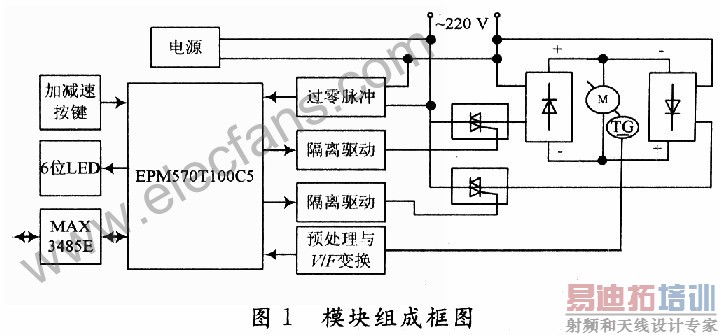

模块组成框图如图1所示。主回路可控元件选用双向可控硅,成本低、控制电路简单、调压方便可靠。为实现电机双向运行,采用两组反并联的整流单元。双向可控硅调压后经桥式整流模块变换成直流电,输出给电动机进行调压调速。调压采用移相方式,所以设计了电源过零脉冲形成电路。为增加模块可靠性,强电与弱电全部用光电耦合器隔离;双向可控硅单元内有简单的RC缓冲电路,用以抑制du/dt。考虑到某些应用场合需要远程控制,增加了RS 485通信单元,用MAX3485E芯片进行电平转换。测速选用直流测速发电机,相对于光电编码器更经济,测速发电机输出的直流电压经降压、滤波预处理后进行V/F变换。6位LED显示当前速度。电源电路为整个系统提供+3.3 V电源。

主控芯片EPM570T100C5是Altera的MAXⅡ系列低成本的复杂可编程逻辑器件((2PLD)产品,其密度高且性能优良,内置用户非易失性FLASH存储器块,内部时钟频率高达300 MHz,100脚MBGA封装,570个逻辑单元(LE)。MAXⅡ器件具有创新的查找表(LUT)逻辑结构,突破了传统宏单元器件的成本和功耗限制。设计人员可以利用MAXⅡ器件来替代低密度FPGA,ASSP和标准逻辑器件,支持在系统编程(ISP),很容易在现场重新进行配置。使用EPM570T100C5开发调速装置,大大降低了系统功耗、体积和成本。另外,Altera提供免费的QuartusⅡ基础版软件,支持所有MAXⅡ器件,它是基于MAXⅡ器件引脚锁定式装配和性能优化而设计的。

2 可控硅调压调速原理

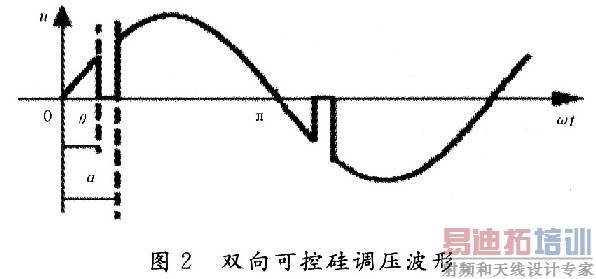

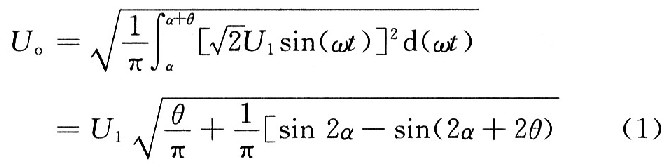

移相触发就是通过改变晶闸管每周期导通的起始点即触发延迟角α的大小,达到改变输出电压、功率的目的。图2给出了双向可控硅调压波形,电源电压![]() ;α为移相角;θ为导通角。输出电压与控制角关系见式(1),移相范围φ≤α≤π。

;α为移相角;θ为导通角。输出电压与控制角关系见式(1),移相范围φ≤α≤π。

式中:α和θ满足![]() ;负载阻抗角为φ=arctan(ωL/R);L为主回路总电感;R为主回路总电阻。

;负载阻抗角为φ=arctan(ωL/R);L为主回路总电感;R为主回路总电阻。

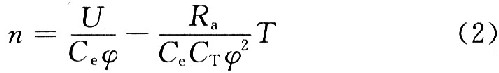

双向可控硅输出电压整流后加到主电机电枢回路,构成降压调速系统,调压调速机械特性硬度不变,调速范围大,能量损耗小。电压与速度关系满足式(2)的机械特性。

式中:U为电机电枢电压,来自双向可控硅输出电压U0;Ra为电枢回路电阻;T为电磁转矩;φ为每极磁通;Ce为电动势常数;CT为转矩常数。

设磁通保持不变,电枢电路中也没有串联可调外电阻,减小电动机电枢供电电压时,由于转速不立即发生变化,反电动势也暂不发生变化,此时电枢电流减小,转矩也减小,若阻转矩未变,则合成转矩小于零,转速下降,反电动势减小,电枢电流和电磁转矩也随之增大,直到达到转矩平衡时为止,但此时转速已较原来的降低了。由于调速时磁通不变,故也为称之恒转矩调速。

3 FPGA核心设计

3.1 主模块

采用自顶向下的设计方法,主模块原理图如图3所示。包括speed_detection为速度检测、speed_control为速度控制、RS 485为串口通信、gate_control为主控子模块4部分。speedpulse为V/F转换后的速度脉冲信号;start和stop分别为起动和停止按键的输入信号;inc和dec分别为加减速按键的输入信号;zeroin为同步过零脉冲的输入信号;rxd,txd,notre和de连接到RS 485接口芯片MAX3485E;alarm为超速报警信号;led0~led5为速度显示6位数码管的输出信号;maincj为主接触器的控制信号;redled和greenled分别为红绿灯输出信号;pulse I和pLalseⅡ为正反组双向可控硅控制信号。

[p]

[p]

速度检测子模块在单位时间内对speedpulse计数,得到速度值speedvalue,并经过译码送到6位LED显示。速度控制模块根据设定速度和检测速度用PID算法调节输出脉冲,改变移相角来控制速度;设定速度为reg变量,可用inc和dec按键调节,也可以来自RS 485模块;根据速度设定值的正负得出direction信号,控制脉冲信号加在两组双向可控硅之一,使电机正反两方向转动。主控子模块负责控制整个系统的起动和停止,复位各个子模块,提供1 Hz,25 600 Hz,10 Hz脉冲信号。RS 485模块负责通信管理、解析通信协议,从而接收16位速度设定值。

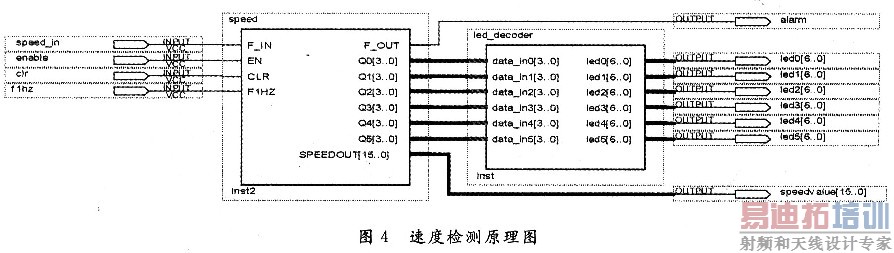

3.2 速度检测

速度检测模块主要包括频率计和译码电路,如图4所示。enable为速度检测使能信号,clr为输出清零信号,speed_in为输入速度脉冲信号,led0~led5为6位数码管输出信号。

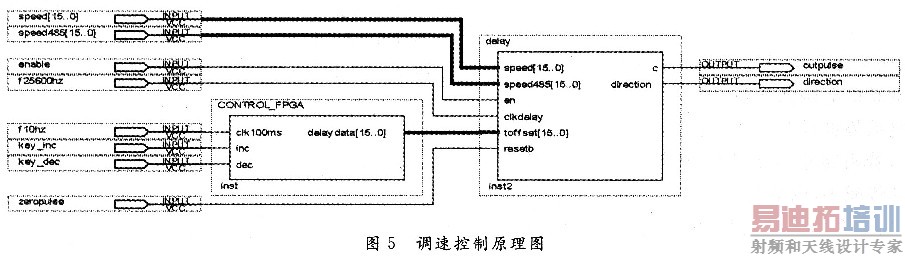

3.3 速度控制

速度控制的原理是根据设定速度与实际速度的偏差用PID算法产生控制量,根据控制量的大小把过零检测脉冲移相后加宽作为输出控制信号,如图5所示。

enable为输入使能控制信号;f25600hz为决定移相单位时间的输入信号;delay_flhz为按键加减的单位时间输入信号;key_inc和key_ dec分别为加速和减速按键的输入信号;zeroin为输入同步过零脉冲信号,频率为100Hz;outpulse为输出的移相脉冲信号;direction为转向信号。

3.4 RS 485通信模块

RS 485总线是一种多点差分数据传输的电气规范,其通信接口允许在简单的一对双绞线上进行多点双向通信,具有噪声抑制能力强,高速数据传输,且电缆比较长及可靠性高的特点。

RS 485子模块主要实现UART功能,并通过notre和de信号控制发送和接收。串行通信固定设为9 600波特、8位数据、无奇偶校验、1位停止位。数据格式:地址码、数据、结束字符,其长度分别为8位、16位、8位。当总线上挂接多个调速模块时,采用广播方法发送消息,地址码可根据实际情况约定。由于RS 485总线是异步半双工的通信总线,一个时刻总线只可能呈现一种状态。因此在空闲状态时,将RS 485总线始终设置为接收状态。3.5 仿真

功能仿真又称前仿真,其目的是检查HDL代码所描述的逻辑功能是否和预期的功能一致。全部模块已在QuartusⅡ中仿真通过,图6给出速度控制模块功能仿真波形。仿真时间为30 s,假设期间实际速度为常数,在3.9 s按下加速按键,使key_inc变为高电平,10 s后(13.90 s时刻)加速按键释放变为低电平,据图6的仿真波形图中可知,在13.90 s时刻,输出脉冲下降沿相对于过零脉冲从180°向前移相约70°,表明移相调速功能正常。 [p]

4 实际系统运行数据

为调试和分析系统运行状况,测得如表1所示系统运行数据。主电动机型号110ZF53,pN=100 W,UN=220 V,IN=0.50 A,1 600 rpm。 delaydata[15..8]是速度控制模块中元件CONTROL FPGA的延时,输出数据高8位。

从表1中数据看出,控制系统可有效、连续地调整电机速度,稳态误差较小,负载转矩的变化使移相角与转速之间呈非线性关系,但移相角与输出电压——对应。

5 结语

该设计具有通用性、经济性、可靠性,是常规直流速度控制的较好解决方案。由于采用CPLD芯片作为控制核心,可方便地进行各种改进。若要进一步提高控制性能,可以增加电流闭环;或稍加改动,可以控制两台直流电机的单向运行;可以实现组成分布式网络控制系统等。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:如何应对数据通信爆炸性增长

下一篇:基于CPLD的水下冲击波记录仪的设计