- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用FPGA解决65nm芯片设计难题

随着工艺技术向65nm以及更小尺寸的迈进,出现了两类关键的开发问题:待机功耗和开发成本。这两个问题在每一新的工艺节点上都非常突出,现在已经成为设计团队面临的主要问题。在设计方法上从专用集成电路(ASIC)和专用标准产品(ASSP)转向可编程逻辑器件(PLD)将有助于解决这些问题。

过去,半导体行业一直关注的两个目标是缩小体积和提高速率。近40年来,对这些目标的追求促使行业发展符合摩尔定律,性能和电路密度每18个月翻倍。导致技术高速发展,蕴育了计算机革命、互联网革命以及现在的无线通信革命。

但同时也为此付出了代价。一种代价是物理上的。工艺技术上的每一次进步都使得芯片晶体管的“关断”电流增加,也就是待机功耗在增加。另一代价是金钱。每一工艺节点的开发成本呈指数增加。65nm时代的设计必须解决这些代价问题。

人们采用了很多系统级和芯片级方法来处理动态功耗。在系统级上,采用动态功耗管理技术,确保只对工作电路上电,大大降低了器件的平均功耗,从而减少了和功耗相关的问题。

工艺上的进步降低了芯片级的动态功耗。

一是缩小了晶体管体积,减小了晶体管的等效电容(C)。因此,缩小体积使动态功耗随之线性下降。同样,减小供电电压会使动态功耗呈指数下降,是降低动态功耗的重要措施。0.9V~1.0V范围内的供电方式几乎都采取了这一措施来降低功耗。

降低动态功耗的另一工艺进步是在130nm工艺上引入了全铜互联和低K金属层绝缘技术。这些工艺创新大大降低了互联阻抗和电容,不但减小了晶体管开关功耗,而且还降低了芯片信号和内部电源走线的IR压降。

动态功耗下降而漏电流增大

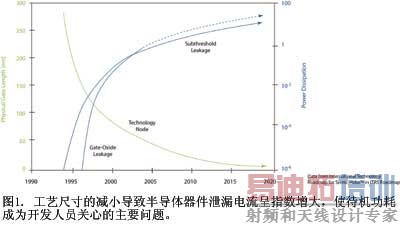

然而,半导体物理规律却表明工艺尺寸下降对待机功耗有不利的影响。工艺尺寸缩小后,随着晶体管逻辑门厚度和沟道长度的减小,这些晶体管的栅极和漏极泄漏电流呈指数增大(图1),而这是影响待机功耗的主要因素。通过使用较长的沟道以及较厚的氧化层来控制泄漏电流将导致开关速率下降,因此,工艺开发人员不得不折衷考虑速率和功耗。

[p]

[p]

工艺尺寸缩小,连线的宽度和高度也随之减小,对功耗有不利的影响。减小铜连线的尺寸增强了电子散射和粒子边界效应。从而增大了连线阻抗,导致电路延迟和IR压降增大。在45nm以下,这些效应会更加明显。

工艺尺寸不断缩小的结果之一是导致待机功耗成为芯片总功耗中的重要因素。同时,芯片用户关心的问题从动态功耗转向待机功耗。由于待机功耗的增大,许多通信器件分开考虑总功耗预算和待机功耗预算,并逐步增加待机功耗预算的比例。由于这些器件大部分时间处于待机模式,因此,待机功耗成为最主要的问题。

与动态功耗不同,还没有简单的方法来降低待机功耗。芯片开发人员不得不使用复杂的工艺和电路设计方法,牺牲晶体管速率来提高Vt,并采取延长沟道长度等措施。

目前已经有技术突破来解决速率和待机功耗的问题。一种是应变硅,该技术将空穴和电子对的移动能力提高了50%,从而提升了器件速率。与其它技术进步不同,应变硅虽然提高了速率,但是并没有增加待机功耗。然而,它必须在芯片设计中采用新的布版规则,要求较严,导致了限制设计规则(RDR)这一概念的产生。RDR和可制造设计(DFM)在65nm以及更小工艺尺寸上越来越重要。

设计规则使开发过程越来越复杂

DFM重要性的增加以及RDR的出现导致芯片设计更加复杂。物理设计尤其需要更多的资源和简捷的物理设计自动工具。这些规则妨碍了版层重用,增加了新技术采用硬件IP模块的难度。结果导致在芯片设计上加大投入,需要更多的资源来处理新技术中的布版和设计问题。

除了越来越高的开发成本以外,芯片开发人员还面临其它的成本难题。65nm器件仅模板成本就高达2百万美元,而45nm器件模板成本会超过3百万美元。理想情况下,强大的财务支持是任何业务投入的基础,包括芯片开发计划等。然而,很多芯片开发项目缺乏足够的资金支持。

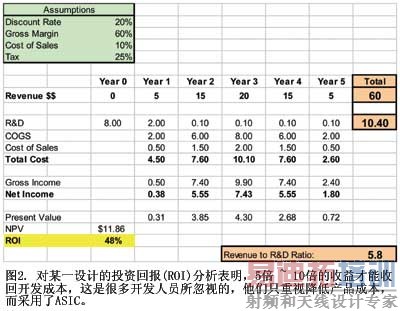

为了很好地进行财务分析,开发人员必须考虑时间、风险、收益和成本等一系列因素。尽管这看起来很难,但可以归结为经过认真设计的投资回报(ROI)分析(图2)。在很多情况下,分析表明,产品生命周期的总收益应是研发投入的5倍~10倍,这样才能收回开发成本。简单地看一下以收益百分比表示的研发开支(10%~20%),大部分成功的公司都会得出相同的结论。

[p]

但是,很多产品开发团队仍然习惯于使用原来的开发方法,忽视了这一简单却生动的结果。特别是,他们不顾风险、收益和成本因素,还在建立ASIC,而ASIC开发在这些方面都有不利影响,最明显的是收益和成本。对于收益问题,业界在上世纪90年代后期和2000年早期过于乐观ASIC器件的量产能力,仅采用产量这一因素来衡量应用开发,结果在财务上失败了。在某些情况下,还是有人不考虑我们已经提到的成本问题,仍然保持一副乐观的态度。

FPGA在总成本上胜出ASIC

65nm和后续工艺节点上需要考虑的是合理的资金分配,而ASIC设计方法成本高,预期收益回报较低。设计人员应认真考虑使用现场可编程门阵列(FPGA)。这些器件解决了当今设计人员面临的功耗问题,有较好的ROI。

对于迫切的功耗问题,Altera高端65nm Stratix III系列FPGA通过各种方法来帮助开发人员降低功耗。为了使开发人员能够在功耗需求和电路性能上达到平衡,Stratix III系列为开发人员提供了全面可编程开发环境,结合其多阈值晶体管和逻辑门长度可变晶体管技术,以及超薄和三门氧化层等技术,不但保持甚至提高了性能,而且把泄漏功耗降到了最低。

Stratix III系列的体系结构含有高性能自适应逻辑模块(ALM)以及多路互联,降低了功耗需求。它还采用了两种创新的低功耗技术。可编程功耗技术使Stratix III中的每一可编程逻辑阵列模块(LAB)、DSP模块以及存储器模块能够独立工作在高速或者低功耗模式下,利用Quartus II软件的PowerPlay功

能,根据性能需要,自动控制每个模块的工作模式。另一功耗优化技术是可选内核电压,设计人员利用该技术可以为高性能应用选择1.1V内核电压,针对低功耗应用选择0.9V内核电压。所有这些特性使FPGA能够在设计上平衡速率和功耗,开发人员不必在某一方面作出牺牲。

对于迫切的资金问题,在综合考虑产品研发成本以及货物售出成本(COGS)后,FPGA是开发人员在ASIC替代方案上的最佳选择。在当今竞争激励的市场上,COGS是决定产品收益和毛利润的主要因素,许多设计人员在考虑FPGA时非常重视它。

FPGA设计的研发成本要比ASIC低几个数量级,开发人员设计FPGA时,不用面对数百万美元的模板成本,不需要在晶体管级单元布局布线上的高级专业技能,也不需要昂贵的自动设计工具和工艺库。Altera Quartus II软件等全面的开发工具处理设计中的物理细节问题,使用户能够将精力集中在系统级设计上。

FPGA的可编程能力还避免了今后大量的研发开支。在产品生命周期中,如果需要在已有设计中加入新功能,对FPGA重新进行编程便可以简单地实现功能改进。而对ASIC设计进行微小的改动也需要在新模板上投入大量人力物力。

认识到可编程优点的开发人员可能会考虑基于处理器的ASIC设计方法。在这一方面,FPGA同样具有优势。可编程逻辑在实现功能上效率要比软件高得多,和基于处理器的设计相比,不但降低了功耗,而且提高了任务执行速度。在基于处理器的设计中,FGPA的确经常被用作硬件加速器。

各种客户群大量采用FPGA,使FPGA的产效在消费类设计上和大批量ASIC水平相当。量产也使得FPGA供应商有足够的收益来切实投入研发。结果,FPGA在体系结构、设计和工艺上是目前最先进的技术,足以和最好的ASIC进行竞争。而且,研发上的投入也保证了FPGA成为功能更强大、质量更好的可靠器件。

对量产的预测已经得到证实。在过去几年中,FPGA的收益超出了半导体市场的总体水平,而且有加速发展的趋势,原因在于芯片技术的复杂度越来越高,业界大量应用降低了对产品量产的预期。所有因素都对FPGA更加有利,而非ASIC。

随着半导体技术在65nm上的突破,人们越来越关心功耗和开发成本问题。使用这些技术的芯片物理设计遇到了更多的挑战,ASIC设计方法实现起来更加困难。设计人员转向基于FPGA的设计后,能够从芯片物理设计难题中抽身而出,让FPGA公司去解决这些问题,把精力集中在应用和系统设计的核心能力以及价值定位上。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:开发集成式DSL

STB所面临的挑战

下一篇:LED路灯电源的选择要素