- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于填谷电路的恒流式LED 高压驱动电源的设计

0 引言

近年来,LED灯具(含LED和驱动电源)作为一种节能环保型照明灯具正在迅速推广,被广泛用于阅读灯、手电筒、汽车方向灯、小型聚光灯,标牌、建筑轮廓及穹顶照明、便携式闪光灯、医疗照明及装饰照明灯等领域。如何降低LED驱动电源的总谐波失真,提高其功率因数,具有重要的现实意义。

1 功率因数与谐波失真

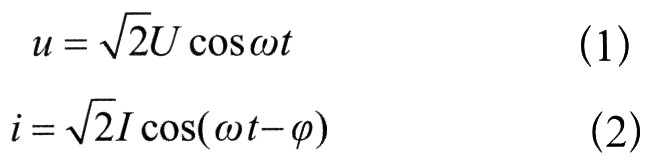

对无失真的交流电而言,其输入电压与输入电流的表达式分别为

式中的u、i均代表瞬时值,U、I为有效值,ψ表示相角。交流输入的视在功率S=UI,而有功功率P=UIcosψ。仅当cosψ达到1时,P=UI=S。

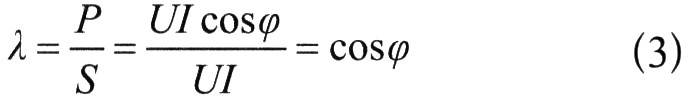

功率因数的英文缩写为PF(Power Factor),其国标符号为λ。功率因数定义为有功功率与视在功率的比值:

交流供电设备的功率因数是在电流波形无失真的情况下定义的。造成功率因数降低的原因有两个:一是交流输入电流波形的相位漂移,二是交流输入电流波形存在失真。相位漂移通常是由电源的负载性质(感性或容性)而引起的,在这种情况下对功率因数的分析相对简单,一般可用公式cosψ=P/(UI)来计算。但是当交流输入电流波形存在失真时,式(3)不再适用。

目前,采用AC/DC变换器的开关电源均通过整流电路与电网相连接。其输入整流滤波器一般由桥式整流器和滤波电容器构成,二者均属于非线性元器件。由于大容量滤波电容器的存在,使得整流二极管的导通角变得很窄,仅在交流输入电压的峰值附近才能导通,致使交流输入电流产生严重失真,变成为尖峰脉冲。这种电流波形中包含了大量的谐波分量,不仅对电网造成污染,还导致滤波后输出的有功功率显著降低,使功率因数大幅度降低。普通AC/DC变换器的功率因数较低,只能达到0.6左右。因此,提高开关电源的功率因数不仅能降低线路损耗、还能减少电网的谐波污染,提高电网的供电质量。

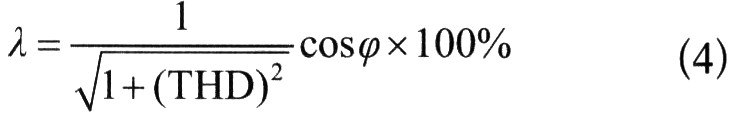

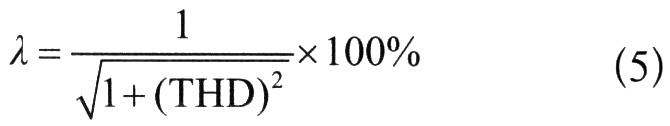

总谐波失真是指用信号源输入时,输出信号(谐波及其倍频成分)比输入信号多出的谐波成分,一般用百分数表示。功率因数(λ)与总谐波失真(THD)存在下述关系:

当交流输入电流与电压保持同相位,且cosψ=1时,式(4)可简化为

利用功率因数校正器PFC(Power Factor Corrector),可使交流输入电流与交流输入电压保持同相位并滤除电流谐波,将设备的功率因数提高到接近于1的某一预定值。功率因数校正分无源功率因数校正(PPFC)、有源功率因数校正(APFC)两种类型。无源功率因数校正的特点是电路简单,成本低廉。

[p]

2 基于无源填谷电路的9W可调光LED高压驱动电源

如上所述,开关电源的输入整流滤波电路所采用的整流二极管和滤波电容均属于非线性元器件,在交流输入正弦波电压为u时,交流输入电流i的波形会发生严重失真,变成了尖峰脉冲,如图1所示。其特点是整流二极管的导通角显著变小,尽管电流有效值大,但电流平均值明显变小。例如,普通硅整流桥的响应时间大约为3ms,而50Hz交流电的半周期只有10ms,仅此一项即可使桥臂上整流二极管的导通时间减小到7ms,所对应的导通角就从理想情况下的180°减至126°。

为此,可在AC/DC变换器的输入级增加功率因数校正电路。 “填谷电路”(Valley FillCircuit)就属于一种新型无源功率因数校正电路,其特点是利用整流桥后面的填谷电路来大幅度增加整流管的导通角,通过填平谷点,使输入电流从尖峰脉冲变为接近于正弦波的波形,将功率因数提高到0.9左右。与传统的电感式无源功率因数校正电路相比,其优点是电路简单,功率因数补偿效果显著,并且在输入电路中不需要使用体积笨重的大电感器。

由LinkSwitch-TN系列产品LNK306P构成的基于无源填谷电路的9W恒流式LED高压驱动电源如图2所示。该电路主要有以下特点:

(1)电路简单,成本低廉。将无源填谷整流滤波电路与LNK306P相匹配,实现功率因数校正。当交流输入电压范围为108~132V时,可将功率因数提高到0.92以上,最高可达0.965(所对应的交流输入电压为90V)。满载条件下的电源效率超过85%。

(2)在交流输入端使用了复式EMI滤波器(C1、L1、L2和C2),R1、R2为泄放电阻。

(3)利用晶体管(VT,2N3906)电路实现欠电压保护。 [p]

(4)在整流桥与填谷电路之间增加了隔离二极管VD5。

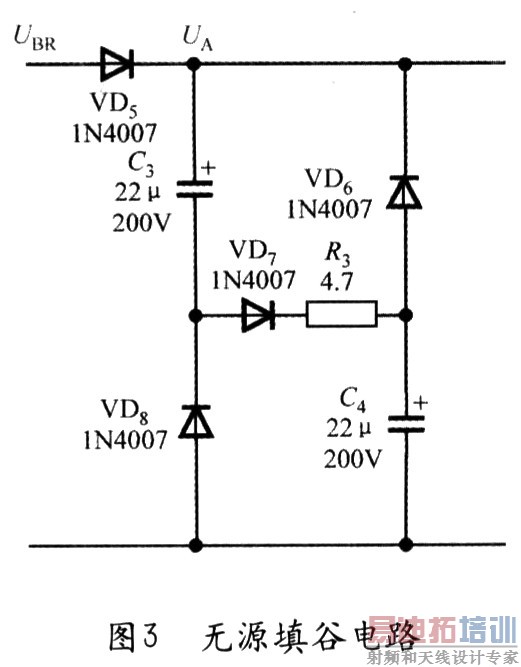

全部由无源元器件构成的无源填谷电路如图3所示。总共仅需使用3只二极管(VD6~VD8)、两只电解电容器(C3、C4)和一只电阻器(R3)。 VD6~VD8采用1N4007型硅整流管。C3与C4的容量必须相等,均采用22μF/200V的电解电容器。R3选用4.7Ω、2W的电阻器,开机时可限制C3、C4上的冲击电流。填谷电路的特点是C3和C4以串联方式充电,而以并联方式进行放电。VD5为隔离二极管,可将整流桥与填谷电路隔离开。设交流输入电压的有效值为u,峰值电压为UP,整流桥输出的脉动直流电压为UBR,VD5右端电压为UA(此即C3和C4上的总电压)。

阶段一:在交流电正半周的上升阶段,由于UBR>UA时,VD2、VD3、VD5和VD7均导通,UBR就沿着C3→VD7→R3→C4的串联电路给C3和C4充电,同时向负载提供电流。其充电时间常数很小,充电速度很快。

阶段二:当UA达到UP时,C3、C4上的总电压UA=UP;因C3、C4的容量相等,故二者的压降均为UP/2。此时VD7导通,而VD6和VD8被反向偏置而截止。

阶段三:当UA从UP开始下降时,VD7截止,立即停止对C3和C4充电。

阶段四:当UA降至UP/2时,VD5、VD7均截止,VD6、VD8被正向偏置而变成导通状态,C3、C4上的电荷分别通过VD6、VD8构成的并联电路进行放电,维持负载上的电流不变。 [p]

不难看出,从阶段一一直到阶段三,都是由电网供电,除了向负载提供电流,还在阶段一至阶段二给C3和C4充电;仅在阶段四由C3、C4上储存的电荷给负载供电。

进入负半周后,在VD5导通之前,C3、C4仍可对负载进行并联放电,使负载电流基本保持恒定。对于VD1、VD4和VD5导通后的情况,读者可参照上文自行分析。

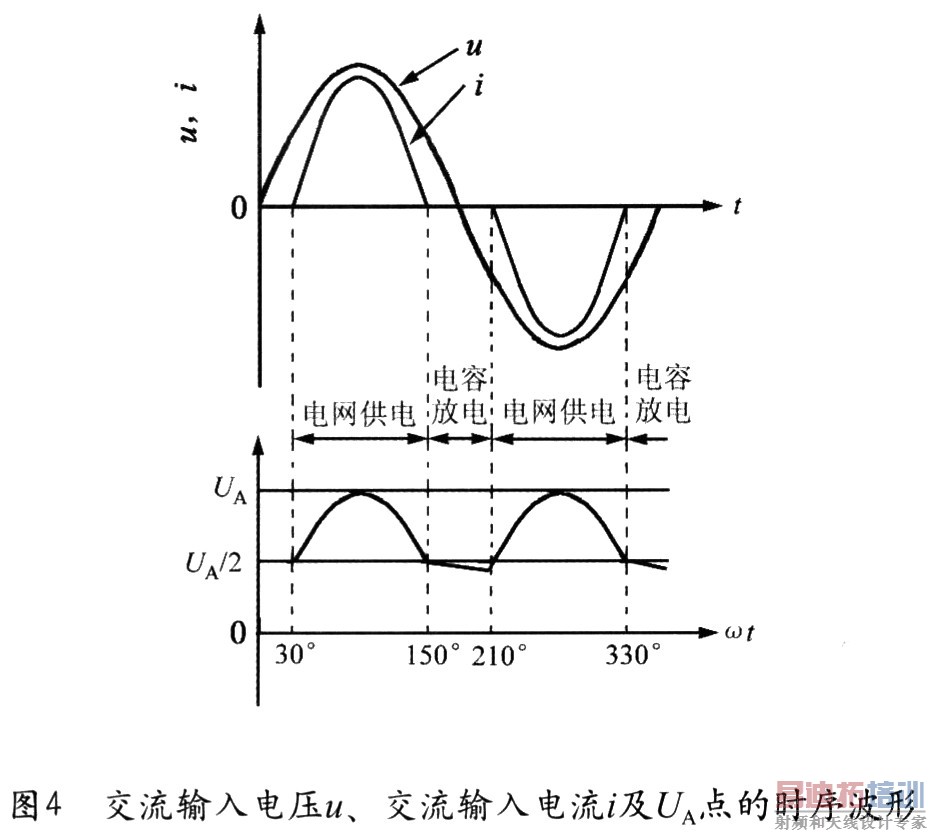

综上所述,利用图3所示无源填谷电路,能大幅度增加整流管的导通角,使之在正半周时的导通角扩展到30°~150°(30°恰好对应于UA= UPsin30°=UP/2,150°对应于UA=UPsin150°=UP/2)。同理,负半周时的导通角扩展为210°~330°。这样,波形就从窄脉冲变为比较接近于正弦波。这相当于把尖峰脉冲电流波形中的谷点区域“填平”了很大一部分,故称之为填谷电路。实测该LED驱动电源的功率因数λ≥0. 92,完全符合能源之星国际节能标准,并且达到EN55015B国际标准对EMI的限定指标。交流输入电压u、交流输入电流i及UA点的时序波形对照如图 4所示。

当MOSFET导通时,VD9处于反向偏置而截止,电流途经输出滤波电容C4、负载及储能电感L2,在向负载提供恒定电流的同时,还有一部分电能储存在 L2上。当MOSFET关断时,L2产生的反向电动势使VD9导通。L2上的电能就通过VD9向负载继续供电,并对C8充电。LNK306P采用开/关控制法。当反馈到FB端的电流超过49μA时,禁止MOSFET在该开关周期内工作;进入下一开关周期后,再次对FB端的电流采样,若电流小于49μA,则允许MOSFET工作。对输出电压的调节就是通过禁止(跳过)或使能开关周期来完成的。

4 结束语

利用填谷电路来增加整流管的导通角,使输入电流波形从尖峰脉冲变为接近于正弦波,能大幅度地提高功率因数,显著降低总谐波失真。该设计方案对于设计节能环保型LED灯具的驱动电源具有实用价值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...