- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PADS Logic 逻辑封装引脚位置显示偏差,麻烦指点

录入:edatop.com 点击:

以前使用Orcad画原理图,现在公司要求用pads Logic画原理图,刚刚接触一个多月,还有好多地方不明白,先把遇到的问题给大家描述一下:

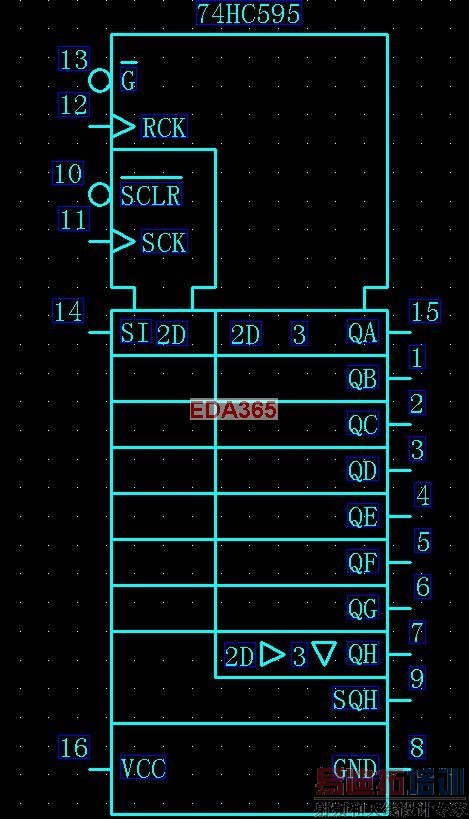

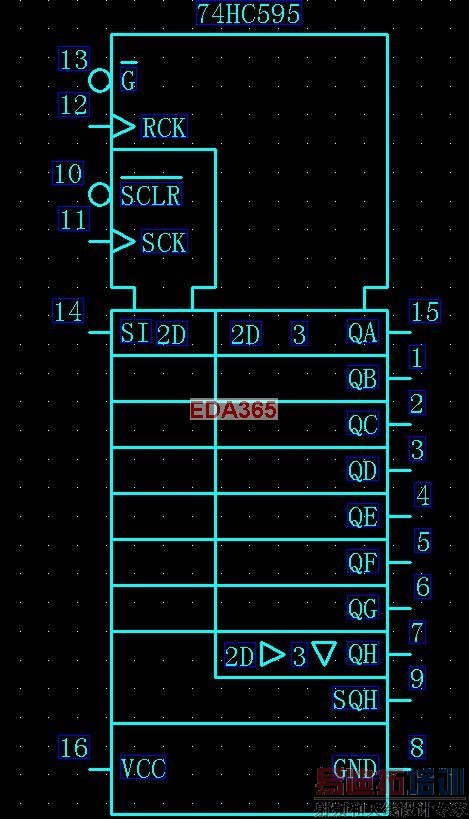

因为公司刚成立不久,所以现在大家也是在共同学习使用PADS软件,我再我的电脑上用Logic制作逻辑封装时,元件引脚的显示信息是正常的,如下图:

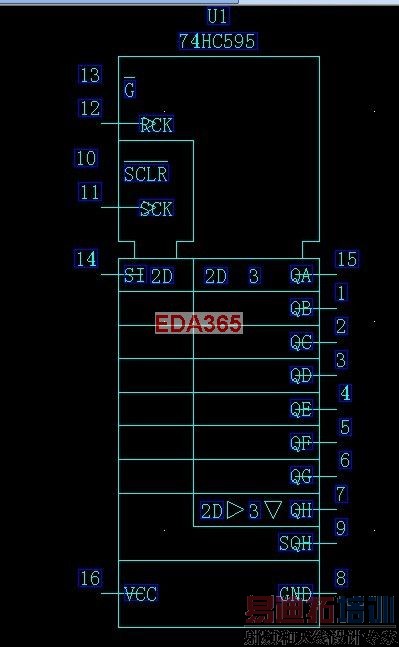

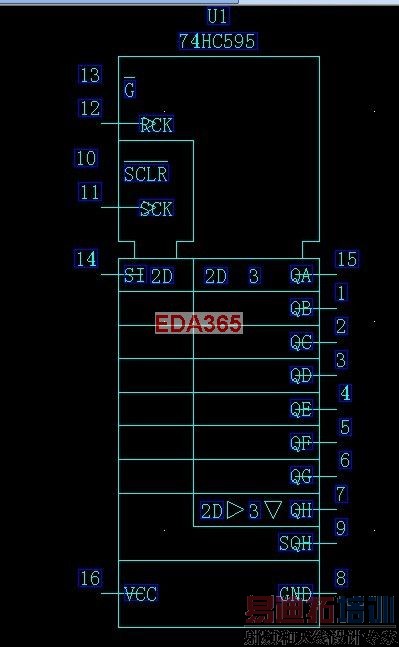

但是在公司另一台电脑上调用这个刚建的元件时,引脚显示有偏差,公司装的是同一个版本的软件,我觉得因该是哪个地方的设置有问题,还请高手指点,谢谢!图片如下:

因为公司刚成立不久,所以现在大家也是在共同学习使用PADS软件,我再我的电脑上用Logic制作逻辑封装时,元件引脚的显示信息是正常的,如下图:

但是在公司另一台电脑上调用这个刚建的元件时,引脚显示有偏差,公司装的是同一个版本的软件,我觉得因该是哪个地方的设置有问题,还请高手指点,谢谢!图片如下:

1,创建logic封装时,应该统一用相同的设计格点和显示格点:如100或50

2,从来没遇到过这种情况,无图无真相.LZ不妨将你们所用的版本还有封装放上来/

谢谢版主回复,我再看一下吧!

认真研究了一下,是因为:pin decal pin not found in library

他们电脑上的库里面没有我只制作封装时用到的引脚封装,

但我不知道软件默认的引脚封装放在那个路径下,所以没办法添加进软件系统的库里面,

所以软件在调用这个封装时还是调用软件本身的PIN Decal,这样引脚位置就会显示有偏差。

请问一下版主是否知道软件自带的PIN Decal放在哪个库里面,找不到,谢谢!

commone路经下可能有些工程师改过参数

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:讨论PADS

下一篇:测试点怎么添加,请各位师傅指教

射频和天线工程师培训课程详情>>