- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

IPTV系统中的FPGA供电问题解决方案

目前越来越多的家用电器从低速的拨号上网向宽带互联网接入或互联网协议电视(IPTV)转移,尤其是IPTV有望在中国获得快速的发展。比较而言,IPTV的基础设施成本相当低,因为这种方法不需要铜轴电缆,而是采用DSL或宽带链接和机顶盒将节目流传送到家用电器。

现在的可编程门阵列(FPGA)已经被证明是这种平台的理想选择,因为它们提供了快速改变市场需求的灵活性。FPGA的电源需求通常很复杂,因为FPGA有多达三种供电要求,为了实现可靠的系统性能,必须对这些要求排序。

内核电压

内核电压轨通常设定成VCCINT,为FPGA逻辑供电。要求的电流从几百毫安到几十安培,具体大小取决于时钟频率和所用的门数。因为该负载是呈高度容性,内核电压电流要求可能在开始的时候很高。FPGA内核对瞬态响应的要求很严格,内核电源电压必须缓慢增加并且常常要求在固定的时间长度内上升到稳定的电压。例如,Xilinx公司的Virtex-4必须让VCCINT电源在0.2ms和50ms之间上电。

I/O电压

I/O电压(VCCIO)通常要求的电压轨是3.3V、2.5V、1.8V或1.5V。I/O标准可以由FPGA中的I/O模块独立设置,因此一个FPGA就有可能存在一个以上的I/O电压。I/O电流要求取决于所用的I/O数量和时钟速度。通常,I/O电流要求低,范围在几百毫安到3A。

辅助电压

辅助电压(VCCAUX)要求电源具有高电源抑制比(PSRR),因为电源直接与数字时钟管理(DCM)相连。如果电源噪声被容许耦合到DCM,将可能影响到系统的性能。

虽然I/O和辅助电压不需要按照特别的顺序上电,但是,FPGA制造商常常要指定内核和I/O的上电顺序或跟踪该顺序。不指定上电顺序或不跟踪上电顺序所面临的后果是常常会对系统中的器件造成不可挽回的破坏。FPGA、PLD、DSP和微处理器通常在内核与I/O电源之间放置二极管作为ESD保护元件。如果电源违反了跟踪要求并超过了保护二极管的正向偏置,那么该器件就可能被损坏。

解决方案

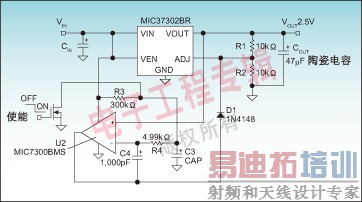

为说明FPGA供电要求的复杂性,以在固定时间段对VCCINT上电的要求为例。为了保证由上下限控制的2ms到50ms之间的上电时间,要实现如图1所示的电路。

图1:MIC37302和分立电路确保受控的斜率和时序

对内核和I/O电源的上电排序或上电顺序的跟踪,增加了电源管理电路的复杂性和成本。为克服这个问题,设计工程师需要一种不增加外部元器件而满足所有这些需要的器件。这种产品的一个例子就是Micrel公司的MIC68200 LDO适用于各种板上电源" target=_blank>LDO ,它把上升速度控制、上电排序和跟踪等功能集成到一个3×3mm的MLF封装之中。

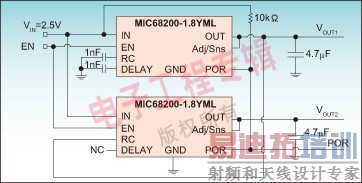

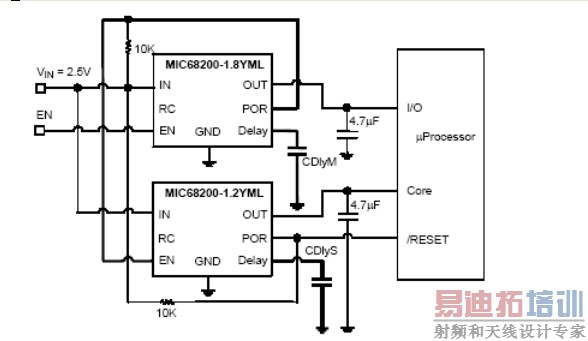

多颗MIC68200可以按两种模式级联:在跟踪模式中,主器件的输出驱动从器件的RC引脚,以便从器件在打开和关闭期间跟踪主稳压器;在顺序上电模式中,主器件的POR驱动从器件的使能(EN)端,以便在主器件打开之后打开,在主器件关闭之前(或之后)关闭。除了具备跟踪能力之外,电压斜坡控制(RC)引脚还能通过一个电容对内核电压轨的斜坡电压进行精确编程。

跟踪及排序电路分别如图2和图3所示,从图中可以看出该解决方案是一种简单且需要很少分立元器件的实现方案。

图2:跟踪电路,内核电压的斜坡由RC引脚上的电容来设置

图3:排序电路,主稳压器的POR使能从稳压器,POR延迟由低电容的设置

本文小结

总之,IPTV视频广播中采用FPGA作为编码和解码平台的好处是明显的。然而,为FPGA供电可能是一个挑战,而采用根据电源要求设计的专用电源管理器件,如MIC68200,将极大地缩短新系统的上市时间。

作者:

Ralph Monteiro

产品行销经理

Micrel公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:用LTB技术改善多相直流转换器的响应速度

下一篇:便携产品电源芯片的应用技术