- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

超高速USB 3.0存储端设计三大注意点

在高清画质与蓝光的普及下,USB 3.0大幅减少了档案传输的等待时间。USB 3.0具有向下兼容与超高速两大优势,在系统商与芯片厂商的合作下,我们相信该技术一定会迅速普及。正是由于USB 3.0改变了对传统USB速度较慢的看法,祥硕科技将与大家分享关于USB 3.0存储端设计应注意的事项。

首先,由于祥硕科技提供的产品是属于高速的产品,以目前市场上效能最高的产品ASM1051E为例,主要对外的两个接口分别为USB 3.0端与SATA 6G端,根据目前客户端量产状况,成功设计USB 3.0模块主要有三个要点。

保持高速信号的完整性

信号的质量关系到数据的传输是否完整或U盘的可靠性。根据信号完整性制定出电路板的设计规范及组件的摆放位置,差动传输线阻抗控制,减少阻抗在电路板上所造成的不连续,而引起的信号多重反射及损失,干扰控制与抑制等,确保符合USBIF兼容测量结果。

USB 3.0设计建议如下:差动特征阻抗为85Ω。印刷电路板的贯孔不能多于二个,以减少信号的衰减。一个信号的贯孔约增加1dB的损失。差动信号长度不超过1.5英寸,预防主控端印刷电路板可能导致的信号损失及USB 3.0连接器与电缆的良莠不齐,以达到最佳的效能。差动信号之间的间距最好多加地信号,以减少信号之间的干扰,如信号旁边为频率信号或是切换式电源信号,即再加大3~4倍的间距。在信号交流耦合电容选用0402大小封装及NPO或是X7R材质,且摆放至接近连接器的位置。如有ESD及EMI组件的选用及摆放,则将组件位置也放在接近连接器的位置,建议的顺序为“连接器、ESD、EMI、交流耦合电容、ASM1051E”,注意ESD及EMI的零件选用都要能够符合要求,差动特征阻抗及信号损失非常低。

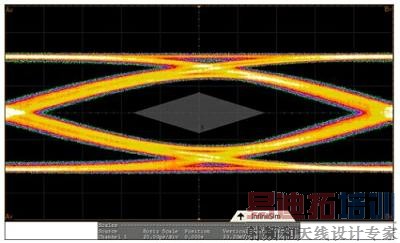

图1:USB 3.0的眼图。

[p]

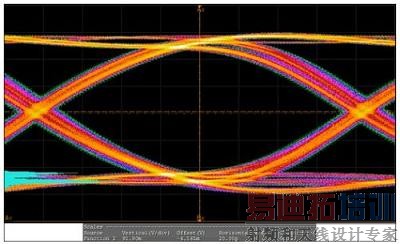

SATA 6G设计建议如下:除了差动特征阻抗为90Ω及长度要求可放宽至2.5英寸之外,其它则与USB 3.0上的建议是相同的。

图2:ASTA 6G的眼图。

电源及导热管理

在新的USB 3.0系统设计上,由于高速传输的关系,其瞬间耗电量较USB 2.0更大,如何能平均传导热能,除了需慎重选择芯片厂商外,在模块的设计上也有其需要加强之处。

设计建议如下:最好使用线性稳压器(LDO),以减少切换式电源噪声干扰及EMI问题,但相对会有转换效率较差的问题及散热需要考虑;电源稳压电容请参照厂商的设计建议,芯片旁的稳压电容只需要选用0402大小封装的0.1μF;ASM1051E已内置一组线性稳压器,采用QFN封装,热阻较小,有利于散热,印刷电路板上散热贯孔的安排,零件层上铜箔裸露均利于将热传导至印刷电路板上;注意设计应在不影响量产组装的前提下实行。

整体BOM成本

设计建议如下:使用线性稳压器;二层印刷电路板即可达到预定的效能;使用普通SATA 1.5G/3Gbps的连接器即能实现6Gbps的效能;单面打件。

除了芯片及USB 3.0标准连接器之外,所有零件包括二层的PCB板都与USB 2.0时相同。

由于USB 3.0是比传统USB 2.0速度高出数倍的产品,在固件、主控端芯片、线缆、接口等方面都有可能因为信号的微小差异而导致不兼容的结果。其系统设计思维也与2.0大不相同,如何兼顾信号质量与成本将会是研发人员的一大考验。希望大家能由本文中获得一些设计的新思维,早日推出USB 3.0产品。

供稿:祥硕科技公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...