- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

什么是并行比较型ADC(模数转换器)

1.转换方式

直接转换ADC。

2.电路结构

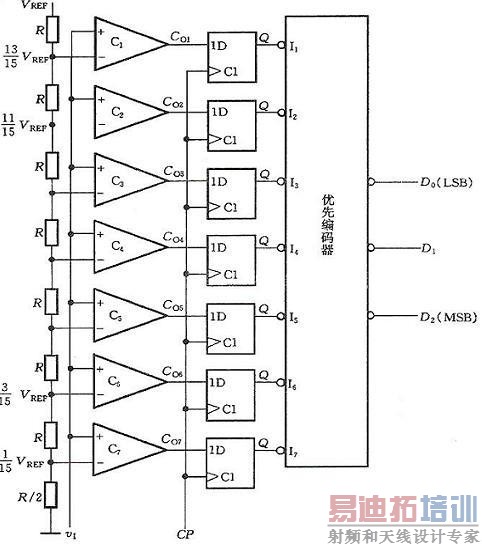

3位并行比较型A/D转换器原理电路如图11.9.1所示。它由电阻分压器、电压比较器、寄存器及编码器组成。

图11.9.1 3位并行A/D转换器

3.工作原理

图中的8个电阻将参考电压VREF分成8个等级,其中7个等级的电压分别作为7个比较器 C1~C7 的参考电压,其数值分别为VREF/15、3VREF/15…、13VREF/15。输入电压为v1,它的大小决定各比较器的输出状态,如当0≤v1< VREF/15时,C7~C1的输出状态都为0;当3VREF/15≤v1<5VREF/15时,比较器C6和C7的输出CO6=CO7=1,余各比较器的状态均为0。根据各比较器的参考电压值, 可以确定输入模拟电压值与各比较器输出状态的关系。 比较器的输出状态由D触发器存储,经优先编码器编码,得到数字量输出。 优先编码器优先级别最高是I7 ,最低的是I1。

设v1变化范围是 0~VREF,输出3位数字量为D2D1D0,3位并行比较型A/D转换器的输入、输出关系如表10.2.1所示。

表11.9.1 3位并行A/D转换器输入与输出关系对照表

| 模拟输入 | 比较器输出状态 | 数字输出 | ||||||||

| CO1 | CO2 | CO3 | CO4 | CO5 | CO6 | CO7 | D2 | D1 | D0 | |

| 0≤v1< VREF/15 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| VREF/15≤v1<3VREF/15 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 3VREF≤v1<5VREF/15 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 5VREF≤v1<7VREF | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

| 7VREF/15≤v1<9VREF/15 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 9VREF/15≤v1<11VREF/15 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 11VREF/15≤v1<13VREF/15 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

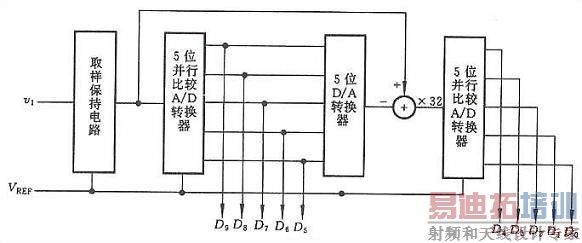

| 13VREF≤v1< VREF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 4.特点 图11.9.2 分级并行转换10位A/D转换器 射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师... 天线设计工程师培训课程套装,资深专家授课,让天线设计不再难... 射频和天线工程师培训课程详情>>

|