- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

数字输入输出端口的平均和最大电流计算

录入:edatop.com 点击:

作者: 王林,Andrey Malkov,Evgeny Shevchenko

摘要

时至今日,随着数字输入输出端口(I/O)逻辑转换速率的提高,电源完整性问题在电路设计中也变得越来越重要。I/O的电源完整性问题主要源自其开关噪声对电源及回路的影响,而电源及回路上的噪声会引起高速数字系统的逻辑错误、电磁辐射、时序延迟和时钟抖动等多种问题。为了分析I/O系统的电源完整性,需要同时考虑I/O口特性、电路板参数和仿真工具的运用【5】【6】【7】【10】。而对整个I/O模块的通用电路模拟程序(SPICE)模型进行仿真,既费时又费力,因此能够快速的估算I/O电流消耗对于项目的前期阶段尤为重要。本文介绍了两个有用的公式可以轻松的估算I/O的平均和最大电流消耗。并以飞思卡尔半导体公司的i.MX6应用处理器为例进行了详细解释。其估算数据与真实的SPICE仿真数据相吻合。

介绍

电源完整性对I/O信号有下面几方面影响:

●信号质量:

信号上存在的噪声是通过信号转换参考时耦合了电源或回路的噪声带来的【8】。

●时序延迟和抖动(推出或推入横向同步开关输出噪声,转换速率影响)【9】:

I/O接口可分为三级,逻辑级、高速I/O级(时钟及其它,如预驱动)和末级(驱动、接收电路)。从内核逻辑到I/O输出级,信号会引入多级延迟。伴随着电压的波动,信号通过每一级的延迟会增加或减少。因此一个边沿从离开内核到它到达I/O口的时间会随着电源及回路的噪声变化而变化。同时,信号边沿也可能受电源及回路的噪声影响变快或变慢。所有这些内部级与末级I/O (驱动、接收)可能共用电源回路网络也可能不共用。当确定供给电源及回路的噪声引发时序变化时,需要考虑可能从其它级耦合的噪声影响。

●功能:

电源及回路上的电压波动会干扰数据锁存,从而导致逻辑错误、数据丢失、切换失败甚至发生系统故障。当噪声引起信号跌落时电压低于最小VIH(输入高的判决门限) 或过冲时电压高于最大VIL(输入低的判决门限)故障就会发生【4】。简单地说,I/O单元平均电流定义的是它的工作模式,最大电流则是指最大瞬态峰值电流。芯片I/O模组对电源供电能力的需求依赖于平均电流值,但计算最大电流也至关重要。系统可靠性设计需要评估IO的瞬态电流,使用电源完整性仿真工具进行瞬态电流消耗分析。在项目前期阶段快速可靠的分析,有助于节约设计开发周期。

I/O平均电流消耗

根据i.MX6应用处理器的数据手册【3】,飞思卡尔提供了一个计算I/O平均电流消耗的公式,如下所示:

Iavg = N x C x V x F, 或者 Iavg = N x C x V x (0.5 x F) (1)

公式中,N代表属于同一电源域I/O模组的管脚数量。 C代表外部等效容性负载。 V代表I/O模组电压值。F代表相应I/O模组或接口的时钟变化率。0.5xF代表数据变化率,最大值为0.5倍的时钟频率F。

在公式(1)中,lavg单位安培,C单位法拉,V单位伏特,F单位赫兹。

其中关键参数是在特定频率下的等效容性负载。负载电容的最大可能值依赖于I/O接口的类型(工业规格需求)或I/O口的工作频率(I/O的最大驱动能力)。

而实际负载电容可以这样计算:C = Cio (I/O管脚和封装的寄生电容) + Cload (传输线和远端输入电容)

其中Cio参数可以从输入输出缓冲器信息规范(IBIS)模型中提取。典型的50欧姆阻抗传输线的等效电容是3皮法每英寸(在实际使用SPICE模型的仿真中会体现)。

下面举例说明如何估算I/O平均电流。

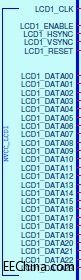

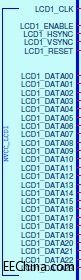

i.MX6平台NVCC_LCD电源域显示接口模组包含29个管脚,如下图所示。

根据I/O库规格书,每个I/O工作在100MHZ频率时可以驱动最大30皮法负载,工作在200MHZ频率时可以驱动最大15皮法负载。最大驱动负载电容值须根据实际工作频率来设置。

当现实应用工作在1080P@60Hz @ 3.3V时,时钟速率约为170MHz。

在这些条件下,每根数据管脚平均电流最大为:

Iavg (数据I/O) = 15pFx3.3Vx0.5x170MHz = 4.2mA (2)

时钟管脚平均电流为:

Iavg (时钟I/O) = 15pFx3.3VX170MHz = 8.4mA (3)

通过公式(2)可以得到在特定频率下数据IO的最大可能平均电流,每周期翻转一次。

SPICE仿真时最大电流的条件是:最佳工艺实例、最高I/O工作电压和最高工作温度。

显示接口的另外三个同步、使能信号的数据速率比较低。我们按照三分之一数据线消耗电流来估算。

复位信号是静态的可忽略(有低阻抗负载除外)。

那么Iavg (全部模组) = 24 (数据信号) x 4.2mA+ 1 (时钟信号) x 8.4mA+4.2mA (同步、使能信号) =113.4mA (4)

合理的估算是值得推崇的,因为一味的出于安全考虑而过高地估计电流消耗会导致电源设计的浪费。

I/O最大电流消耗

下面的公式【1】【2】可以来计算最大电流:

Imax=nCV/tr

其中:

n代表负载的数量

C 代表负载的电容值

V 代表电源供电电压

tr 代表输出信号的上升时间

同样在i.MX6的规格书中可以找到I/O的交流特性参数,如下表所示:

注意:对于IO的配置参数含义,请参考i.MX6应用处理器的参考手册【3】。

通过上表可知在ipp_dse=101、快速的转换速率和15pF负载的测试条件下,最大的tr=1.06ns。

Imax (每个数据管脚) = 15pFx3.3V/1.06ns = 46.7mA

但是对于液晶显示器接口的应用,我们不能直接使用每个管脚的最大电流值乘以总的管脚数量。为了得到合适的估计结果必须考虑实际的数据时序及码型。液晶显示器的规格书里可以查到数据传输时序,但不是所有的管脚会同时发生变化。因此我们可以预估仅24根数据管脚可能同时跳变,那么最大电流计算如下:

Imax (整个模块) = 24(数据管脚) x46.7mA = 1120.8mA (7)

是的没错,瞬态最大电流会超过1安培。不要吃惊,请记住这只是以上应用场景下的极限情况,而且并不是对电源供电能力的要求,需要考虑的是电源完整性性能。

结论

不仅对于板级应用,在芯片的设计阶段I/O管脚和模组的电源完整性性能也是一项重点考量项目。在芯片设计的前期阶段I/O设计团队也需要在具体设计完成之前提前提供电流消耗的估算结果,这样才能使整个芯片各个模块的设计配合无误。对于更复杂更精确的电流消耗分析需要借助电源完整性仿真工具的帮助。本文中级介绍的两个公式可以实现快速估算I/O的平均和最大电流。飞思卡尔的I/O设计和应用团队通过对i.MX系列应用处理器的设计验证,证实了公式可以提供相对精确的估算结果。

References

[1]. Henry W. Ott, (2009). “Electromagnetic Compatibility

Engineering”, ISBN 978-0-470-18930-6pp. 428.

[2]. Lee W. Ritchey, “Right The First Time - A Practical Handbook On High-Speed PCB and System Design”, pp. 353.

[3]. Freescale Semiconductor i.MX6 series applications processors Datasheet at http://www.freescale.com/

webapp/sps/site/prod_summary.jsp code=i.MX6Q&fpsp=1&tab=Documentation_Tab

[4]. Vishram S. Pandit, Woong Hwan Ryu, Myoung Joon Choi, “Power Integrity for I/O Interfaces: With Signal

Integrity/ Power Integrity Co-Design (Prentice Hall Signal Integrity Library)”, ISSBN -13: 970-0-137-01119-3, pp. 1-383.

[5] M. Swaminathan, E. Engin, “Power Integrity Modeling and Design for Semiconductors and Systems”, Prentice

Hall, press.

[6]. M.J. Choi, and V. Pandit, (2009). “SI/PI Co-Analysis for I/O Interfaces,” IBIS Summit.

[7]. Eric Bogatin, (2009). “Signal and Power Integrity – Simplified2nd Edition”, Hardback.

[8]. Masanori Hashimoto & Raj Nair, (2011). “Power Integrity for Nanoscale Integrated Systems”, A practical handbook for designing with power supply noise.

[9]. Vishram S. Pandit and others, (2009). “SSO Noise, Eye Margin, and Jitter Characterization for I/O Power Integrity”, DESIGNCON.

[10]. I. Novak (2008). (Executive Editor), “Power Distribution Design Methodologies” IEC, ISBN: 978-1-931695-65-7.

摘要

时至今日,随着数字输入输出端口(I/O)逻辑转换速率的提高,电源完整性问题在电路设计中也变得越来越重要。I/O的电源完整性问题主要源自其开关噪声对电源及回路的影响,而电源及回路上的噪声会引起高速数字系统的逻辑错误、电磁辐射、时序延迟和时钟抖动等多种问题。为了分析I/O系统的电源完整性,需要同时考虑I/O口特性、电路板参数和仿真工具的运用【5】【6】【7】【10】。而对整个I/O模块的通用电路模拟程序(SPICE)模型进行仿真,既费时又费力,因此能够快速的估算I/O电流消耗对于项目的前期阶段尤为重要。本文介绍了两个有用的公式可以轻松的估算I/O的平均和最大电流消耗。并以飞思卡尔半导体公司的i.MX6应用处理器为例进行了详细解释。其估算数据与真实的SPICE仿真数据相吻合。

介绍

电源完整性对I/O信号有下面几方面影响:

●信号质量:

信号上存在的噪声是通过信号转换参考时耦合了电源或回路的噪声带来的【8】。

●时序延迟和抖动(推出或推入横向同步开关输出噪声,转换速率影响)【9】:

I/O接口可分为三级,逻辑级、高速I/O级(时钟及其它,如预驱动)和末级(驱动、接收电路)。从内核逻辑到I/O输出级,信号会引入多级延迟。伴随着电压的波动,信号通过每一级的延迟会增加或减少。因此一个边沿从离开内核到它到达I/O口的时间会随着电源及回路的噪声变化而变化。同时,信号边沿也可能受电源及回路的噪声影响变快或变慢。所有这些内部级与末级I/O (驱动、接收)可能共用电源回路网络也可能不共用。当确定供给电源及回路的噪声引发时序变化时,需要考虑可能从其它级耦合的噪声影响。

●功能:

电源及回路上的电压波动会干扰数据锁存,从而导致逻辑错误、数据丢失、切换失败甚至发生系统故障。当噪声引起信号跌落时电压低于最小VIH(输入高的判决门限) 或过冲时电压高于最大VIL(输入低的判决门限)故障就会发生【4】。简单地说,I/O单元平均电流定义的是它的工作模式,最大电流则是指最大瞬态峰值电流。芯片I/O模组对电源供电能力的需求依赖于平均电流值,但计算最大电流也至关重要。系统可靠性设计需要评估IO的瞬态电流,使用电源完整性仿真工具进行瞬态电流消耗分析。在项目前期阶段快速可靠的分析,有助于节约设计开发周期。

I/O平均电流消耗

根据i.MX6应用处理器的数据手册【3】,飞思卡尔提供了一个计算I/O平均电流消耗的公式,如下所示:

Iavg = N x C x V x F, 或者 Iavg = N x C x V x (0.5 x F) (1)

公式中,N代表属于同一电源域I/O模组的管脚数量。 C代表外部等效容性负载。 V代表I/O模组电压值。F代表相应I/O模组或接口的时钟变化率。0.5xF代表数据变化率,最大值为0.5倍的时钟频率F。

在公式(1)中,lavg单位安培,C单位法拉,V单位伏特,F单位赫兹。

其中关键参数是在特定频率下的等效容性负载。负载电容的最大可能值依赖于I/O接口的类型(工业规格需求)或I/O口的工作频率(I/O的最大驱动能力)。

而实际负载电容可以这样计算:C = Cio (I/O管脚和封装的寄生电容) + Cload (传输线和远端输入电容)

其中Cio参数可以从输入输出缓冲器信息规范(IBIS)模型中提取。典型的50欧姆阻抗传输线的等效电容是3皮法每英寸(在实际使用SPICE模型的仿真中会体现)。

下面举例说明如何估算I/O平均电流。

i.MX6平台NVCC_LCD电源域显示接口模组包含29个管脚,如下图所示。

根据I/O库规格书,每个I/O工作在100MHZ频率时可以驱动最大30皮法负载,工作在200MHZ频率时可以驱动最大15皮法负载。最大驱动负载电容值须根据实际工作频率来设置。

当现实应用工作在1080P@60Hz @ 3.3V时,时钟速率约为170MHz。

在这些条件下,每根数据管脚平均电流最大为:

Iavg (数据I/O) = 15pFx3.3Vx0.5x170MHz = 4.2mA (2)

时钟管脚平均电流为:

Iavg (时钟I/O) = 15pFx3.3VX170MHz = 8.4mA (3)

通过公式(2)可以得到在特定频率下数据IO的最大可能平均电流,每周期翻转一次。

SPICE仿真时最大电流的条件是:最佳工艺实例、最高I/O工作电压和最高工作温度。

显示接口的另外三个同步、使能信号的数据速率比较低。我们按照三分之一数据线消耗电流来估算。

复位信号是静态的可忽略(有低阻抗负载除外)。

那么Iavg (全部模组) = 24 (数据信号) x 4.2mA+ 1 (时钟信号) x 8.4mA+4.2mA (同步、使能信号) =113.4mA (4)

合理的估算是值得推崇的,因为一味的出于安全考虑而过高地估计电流消耗会导致电源设计的浪费。

I/O最大电流消耗

下面的公式【1】【2】可以来计算最大电流:

Imax=nCV/tr

其中:

n代表负载的数量

C 代表负载的电容值

V 代表电源供电电压

tr 代表输出信号的上升时间

同样在i.MX6的规格书中可以找到I/O的交流特性参数,如下表所示:

注意:对于IO的配置参数含义,请参考i.MX6应用处理器的参考手册【3】。

通过上表可知在ipp_dse=101、快速的转换速率和15pF负载的测试条件下,最大的tr=1.06ns。

Imax (每个数据管脚) = 15pFx3.3V/1.06ns = 46.7mA

但是对于液晶显示器接口的应用,我们不能直接使用每个管脚的最大电流值乘以总的管脚数量。为了得到合适的估计结果必须考虑实际的数据时序及码型。液晶显示器的规格书里可以查到数据传输时序,但不是所有的管脚会同时发生变化。因此我们可以预估仅24根数据管脚可能同时跳变,那么最大电流计算如下:

Imax (整个模块) = 24(数据管脚) x46.7mA = 1120.8mA (7)

是的没错,瞬态最大电流会超过1安培。不要吃惊,请记住这只是以上应用场景下的极限情况,而且并不是对电源供电能力的要求,需要考虑的是电源完整性性能。

结论

不仅对于板级应用,在芯片的设计阶段I/O管脚和模组的电源完整性性能也是一项重点考量项目。在芯片设计的前期阶段I/O设计团队也需要在具体设计完成之前提前提供电流消耗的估算结果,这样才能使整个芯片各个模块的设计配合无误。对于更复杂更精确的电流消耗分析需要借助电源完整性仿真工具的帮助。本文中级介绍的两个公式可以实现快速估算I/O的平均和最大电流。飞思卡尔的I/O设计和应用团队通过对i.MX系列应用处理器的设计验证,证实了公式可以提供相对精确的估算结果。

References

[1]. Henry W. Ott, (2009). “Electromagnetic Compatibility

Engineering”, ISBN 978-0-470-18930-6pp. 428.

[2]. Lee W. Ritchey, “Right The First Time - A Practical Handbook On High-Speed PCB and System Design”, pp. 353.

[3]. Freescale Semiconductor i.MX6 series applications processors Datasheet at http://www.freescale.com/

webapp/sps/site/prod_summary.jsp code=i.MX6Q&fpsp=1&tab=Documentation_Tab

[4]. Vishram S. Pandit, Woong Hwan Ryu, Myoung Joon Choi, “Power Integrity for I/O Interfaces: With Signal

Integrity/ Power Integrity Co-Design (Prentice Hall Signal Integrity Library)”, ISSBN -13: 970-0-137-01119-3, pp. 1-383.

[5] M. Swaminathan, E. Engin, “Power Integrity Modeling and Design for Semiconductors and Systems”, Prentice

Hall, press.

[6]. M.J. Choi, and V. Pandit, (2009). “SI/PI Co-Analysis for I/O Interfaces,” IBIS Summit.

[7]. Eric Bogatin, (2009). “Signal and Power Integrity – Simplified2nd Edition”, Hardback.

[8]. Masanori Hashimoto & Raj Nair, (2011). “Power Integrity for Nanoscale Integrated Systems”, A practical handbook for designing with power supply noise.

[9]. Vishram S. Pandit and others, (2009). “SSO Noise, Eye Margin, and Jitter Characterization for I/O Power Integrity”, DESIGNCON.

[10]. I. Novak (2008). (Executive Editor), “Power Distribution Design Methodologies” IEC, ISBN: 978-1-931695-65-7.

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>