- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

快点PCB∣你知道多少阻抗控制?

1、阻抗控制概念介绍

为区别直流电(DC)的电阻,把交流电所遇到的阻力称为阻抗(Z0),包括电阻(R)、感抗(XC)和容抗(XL)。

特性阻抗又称“特征阻抗”。是指在某一频率下,传输信号线中(也就是我们制作的线路板的铜线),相对某一参考层(也就是常说的屏蔽层、影射层或参考层),其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它实际上是电阻抗、电感抗、电容抗等一个矢量总和。

2、控制PCB特性阻抗的意义

PCB在电子产品中不仅起电流导通的作用,同时也起信号传送的作用;

电子产品的高频、高速化,要求PCB提供的电路性能必须保证信号在传输过程中不发生反射,保持信号完整、不失真;

特性阻抗是解决信号完整性问题的核心所在;

电子设备(如电脑、通信交换机等)操作时,驱动元件(Driver)所发出的信号,需通过PCB信号线到达接收元件(Receiver)。为保证信号完整性,要求PCB的信号线的特性阻抗(Z0)必须与头尾元件的“电子阻抗”匹配;

当传输线≥1/3上升时间长度时,信号会发生反射,须考虑特性阻抗。

3、影响特性阻抗的因素

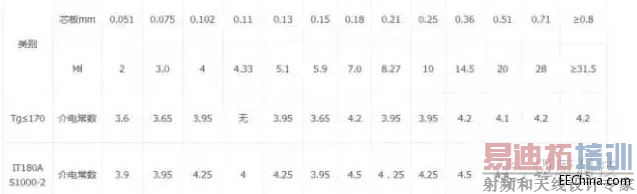

介质介电常数,与特性阻抗值成反比(Er),下图为常规的板材参数:

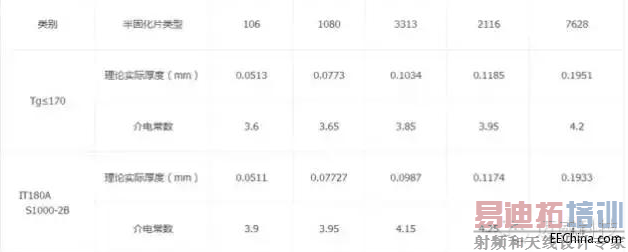

线路层与接地层(或外层)间介质厚度,与特性阻抗值成正比(H),下图为常规的板材参数:

阻抗线线底宽度(下端W1);线面(上端W2)宽度,与特性阻抗成反比。

铜厚,与特性阻抗值成反比(T)

相邻线路与线路之间的间距,与特性阻抗值成正比(差分阻抗)(S)

基材阻焊厚度,与阻抗值成反比(C)

4、影响阻抗的工艺因素

由于蚀刻原因,在铜厚>2oz时对阻抗影响很大,一般无法控制阻抗。

设计中没有铜和线的层面空白在生产时需要用固化片去填充,在计算阻抗时就不能直接代用板材供应商提供的介质厚度,而需要减去固化片填充这些空白地方的厚度,这就是自己计算的阻抗和生产厂家结果不一致的主要原因之一。

5、阻抗的计算

阻抗的计算是相对比较繁琐的,但我们可以总结一些经验值帮助提高计算效率。对于常用的FR4,50ohm的微带线,线宽一般等于介质厚度的2倍;50ohm的带状线,线宽等于两平面间介质总厚度的二分之一,这可以帮我们快速锁定线宽范围,注意一般计算出来的线宽比该值小些。

除了提升计算效率,我们还要提高计算精度。大家是不是经常遇到自己算的阻抗和板厂算的不一致呢?有人会说这有什么关系,直接让板厂调啊。但会不会有板厂调不了,让你放松阻抗管控的情况呢?要做好产品还是一切尽在自己的掌握比较好。

以下提出几点设计叠层算阻抗时的注意事项供大家参考:

a,线宽宁愿宽,不要细。这是什么意思呢?因为我们知道制程里存在细的极限,宽是没有极限的。如果到时候为了调阻抗把线宽调细而碰到极限时那就麻烦了,要么增加成本,要么放松阻抗管控。所以在计算时相对宽就意味着目标阻抗稍微偏低,比如单线阻抗50ohm,我们算到49ohm就可以了,尽量不要算到51ohm。

b,整体呈现一个趋势。我们的设计中可能有多个阻抗管控目标,那么就整体偏大或偏小,不要100ohm的偏大,90ohm的偏小。

c,考虑残铜率和流胶量。当半固化片一边或两边是蚀刻线路时,压合过程中胶会去填补蚀刻的空隙处,这样两层间的胶厚度时间会减小,残铜率越小,填的越多,剩下的越少。所以如果你需要的两层间半固化片厚度是5mil,要根据残铜率选择稍厚的半固化片。

d,指定玻布和含胶量。看过板材datasheet的工程师都知道不同的玻布,不同的含胶量的半固化片或芯板的介电系数是不同的,即使是差不多高度的也可能是3.5和4的差别,这个差别可以引起单线阻抗3ohm左右的变化。另外玻纤效应和玻布开窗大小密切相关,如果你是10Gbps或更高速的设计,而你的叠层又没有指定材料,板厂用了单张1080的材料,那就可能出现信号完整性问题。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:DDRx的关键技术介绍(中)

下一篇:最高境界系列!成功的硬件电路设计心得